总线时序.

25页1、1,5.5 总线时序,时序(Timing)描述各信号随时间的变化及相互间的因果关系。 总线时序描述CPU引脚如何实现总线操作 CPU时序决定系统各部件间的同步和定时,什么是总线操作?,2,5.5.1 基本的总线操作,总线操作是指CPU通过总线对外进行的各种操作 8086的总线操作主要有: 存储器及I/O的读操作 存储器及I/O的写操作 中断响应操作 总线请求及响应操作 总线空闲指CPU正进行内部操作、不进行对外操作的总线空闲状态Ti,什么是总线周期?,3,8086的总线时序(续),任何指令的取指都会产生存储器读总线周期,读取的内容是指令代码 任何一条以存储单元为源操作数的指令都将引起存储器读总线周期,任何一条以存储单元为目的操作数的指令都将引起存储器写总线周期 执行IN指令产生I/O读总线周期,执行OUT指令产生I/O写总线周期 CPU响应可屏蔽中断时产生中断响应总线周期 指令 add bx, ax 将产生那些总线周期?,如何实现同步?,4,8088的总线时序(续),总线操作中的时序同步 CPU总线周期采用同步时序: 各部件都以系统时钟信号为基准 当相互不能配合时,快速部件(CPU)插

2、入等待状态等待慢速部件(I/O和存储器) CPU与外设接口常采用异步时序,它们通过应答联络信号实现同步操作,5,最小组态的总线时序,本节展开微处理器最基本的 4 种总线周期 存储器读总线周期 存储器写总线周期 I/O读总线周期 I/O写总线周期,6,存储器写总线周期 P194,T4,T3,T2,T1,ALE,CLK,A19/S6A16/S3,AD15AD0,A7A0,输出数据,A19A16,S6S3,READY,(高电平),M /IO,WR,7,存储器写总线周期,T1状态输出20位存储器地址A19 A0 , IO/-M输出低电平,表示存储器操作;ALE输出正脉冲,表示复用总线输出地址 T2状态输出控制信号-WR和数据D7D0 T3和Tw状态检测数据传送是否能够完成 T4状态完成数据传送,8,8088 I/O写总线周期,T4,T3,T2,T1,ALE,CLK,A19/S6A16/S3,A15A8,AD7AD0,A15A8,A7A0,输出数据,0000,S6S3,READY,(高电平),IO/M,WR,9,8088 I/O写总线周期,T1状态输出16位I/O地址A15A0,IO/-M输出高

《总线时序.》由会员小**分享,可在线阅读,更多相关《总线时序.》请在金锄头文库上搜索。

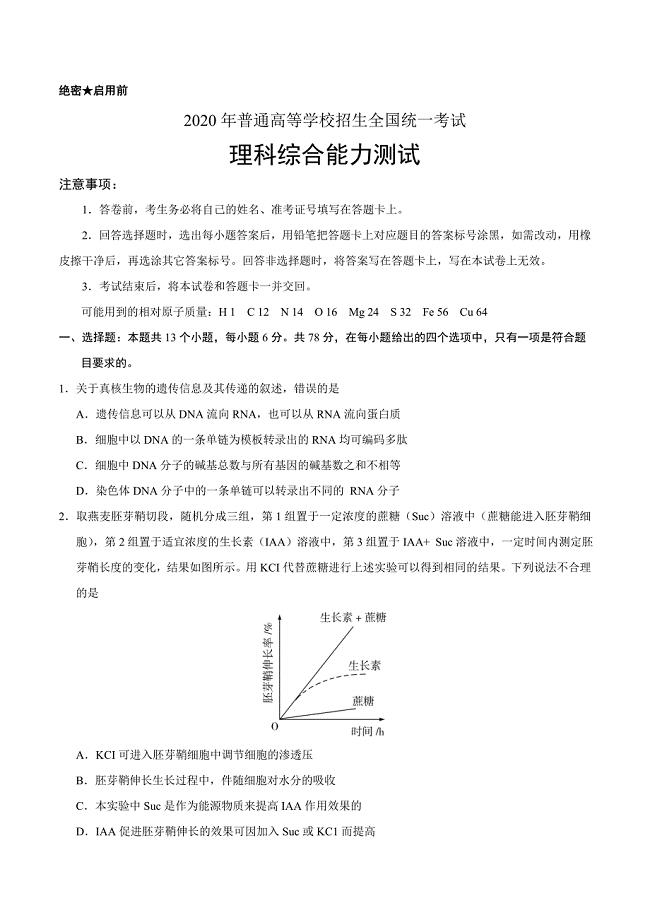

2020年高考真题——理科综合(全国卷Ⅲ)+Word版含答案

2021年绝味鸭脖策划书

2021年熟食店创业方案

2021年熟食店开店策划

2021年卤菜店创业计划书

2021年周黑鸭网络营销策划方案

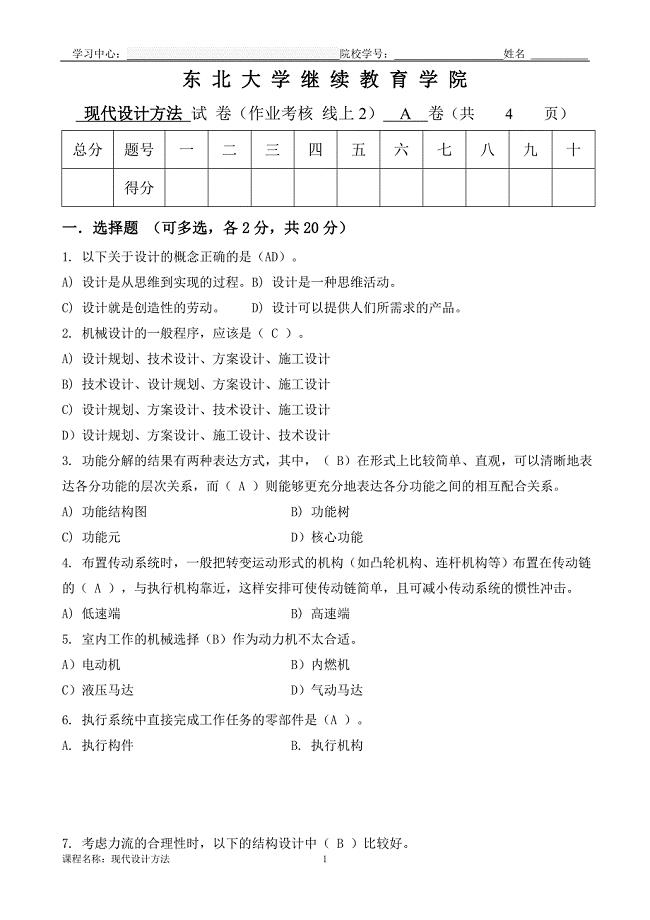

东大21年1月考试《现代设计方法》考核作业

谈我国行政管理效率的现状及其改观对策(论文)

单证员考试-备考辅导-复习资料:无贸易背景信用证案分析.docx

土木工程毕业生答辩自述.docx

建筑学毕业后工作状态真实写照.doc

C#代码规范(湖南大学).doc

xx区食药监局2019年工作总结及2020年工作计划

2019年中医院药物维持治疗门诊工人先锋号先进事迹

2019年度xx乡镇林长制工作总结

2019年性艾科工作计划书

2019年人才服务局全国扶贫日活动开展情况总结

关于组工信息选题的几点思考

摘了穷帽子 有了新模样

2019年某集团公司基层党支部书记培训班心得体会

企业高效开会秘诀

企业高效开会秘诀

2024-01-31 15页

管理者的职责认知

管理者的职责认知

2024-01-31 21页

高效会议秘诀培训PPT

高效会议秘诀培训PPT

2024-01-31 37页

项目管理流程(5大过程)

项目管理流程(5大过程)

2024-01-31 30页

商业分析工具:战略分析与规划工具(精品)

商业分析工具:战略分析与规划工具(精品)

2024-01-31 22页

商业分析工具:由商业问题到最终成果

商业分析工具:由商业问题到最终成果

2024-01-31 48页

管理者的自我成长

管理者的自我成长

2024-01-31 32页

项目管理流程培训PPT

项目管理流程培训PPT

2024-01-31 40页

商业分析工具:销售数据分析方法

商业分析工具:销售数据分析方法

2024-01-31 31页

会议管理知识

会议管理知识

2024-01-31 20页