计算机组成原理 第 4 章 存储器系统(修改版)

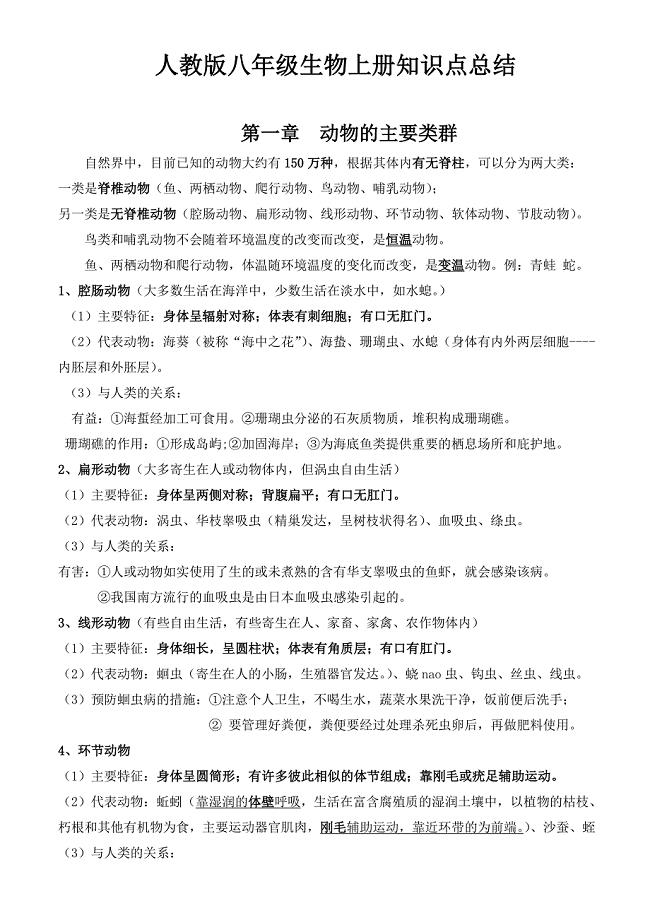

283页1、2019/5/13,第8版 2012.09,1,第四章 存储器系统,2019/5/13,2,本章学习内容 存储器的分类及主要技术指标 存储系统的层次结构 半导体存储器的工作原理 存储器与CPU的连接 辅助存储器的工作原理 Cache的工作原理 并行存储系统,2019/5/13,3,4.1 存储器概述,存储器:计算机的存储部件,用于存放程序和数据。 计算机发展的重要问题之一,就是如何设计容量大、速度快、价格低的存储器。,2019/5/13,4,4.1.1 存储器分类,1按与CPU的连接和功能分类 (1) 主存储器 CPU能够直接访问的存储器。用于存放当前运行的程序和数据。主存储器设在主机内部,所以又称内存储器。简称内存或主存。,2019/5/13,5,(2) 辅助存储器,为解决主存容量不足而设置的存储器,用于存放当前不参加运行的程序和数据。当需要运行程序和数据时,将它们成批调入内存供CPU使用。CPU不能直接访问辅助存储器。 辅助存储器属于外部设备,所以又称为外存储器,简称外存或辅存。,2019/5/13,6,(3) 高速缓冲存储器(Cache),Cache是一种介于主存与CPU之间用于

2、解决CPU与主存间速度匹配问题的高速小容量的存储器。 Cache用于存放CPU立即要运行或刚使用过的程序和数据。,2019/5/13,7,2按存取方式分类,(1) 随机存取存储器(RAM) RAM存储器中任何单元的内容均可按其地址随机地读取或写入,且存取时间与单元的物理位置无关。 RAM主要用于组成主存。,(2) 只读存储器(ROM) ROM存储器中任何单元的内容只能随机地读出而不能随便写入和修改。 ROM可以作为主存的一部分,用于存放不变的程序和数据,与RAM分享相同的主存空间。ROM还可以用作其它固定存储器,如存放微程序的控制存储器、存放字符点阵图案的字符发生器等。,2019/5/13,8,(3) 顺序存取存储器(SAM) SAM存储器所存信息的排列、寻址和读写操作均是按顺序进行的,并且存取时间与信息在存储器中的物理位置有关。如磁带存储器,信息通常是以文件或数据块形式按顺序存放,信息在载体上没有唯一对应的地址,完全按顺序存放或读取。,(4) 直接存取存储器(DAM) DAM是介于RAM和SAM之间的存储器。也称半顺序存储器。典型的DAM就是磁盘。当对磁盘进行信息存取时,先进行寻道,

3、属于随机方式,然后在磁道中寻找扇区,属于顺序方式。,2019/5/13,9,3按存储介质分类,存储介质:具有两个稳定物理状态,可用来记忆二进制代码的物质或物理器件。 目前,构成存储器的存储介质主要是半导体器件和磁性材料。,(1)磁存储器 磁存储器就是采用磁性材料制成的存储器。 磁存储器是利用磁性材料的的两个不同剩磁状态存放二进制代码“0”和“1”。早期有磁芯存储器,现多为磁表面存储器,如磁盘、磁带等。,2019/5/13,10,磁芯存储器,2019/5/13,11,3.5英寸软盘,2019/5/13,12,硬盘,2019/5/13,13,(2)半导体存储器,半导体存储器是用半导体器件组成的存储器。 根据制造工艺不同,可分为双极型和MOS型。,2019/5/13,14,U盘,2019/5/13,15,(3) 光存储器,利用光学原理制成的存储器,它是通过能量高度集中的激光束照在基体表面引起物理的或化学的变化,记忆二进制信息。如光盘存储器。,2019/5/13,16,光盘和光驱,2019/5/13,17,(1) 易失性存储器 电源掉电后,信息自动丢失。如半导体RAM。 (2) 非易失性存储器

4、 电源掉电后,信息仍能继续保存。如ROM、磁盘、光盘等。,4. 按信息的可保存性分类,2019/5/13,18,4.1.2 主存储器的组成和基本操作,2019/5/13,19, 存储元件(存储元、存储位) 能够存储一位二进制信息的物理器件。如一个双稳态半导体电路、一个CMOS晶体管或一个磁性材料的存储元等。存储元是存储器中最小的存储单位。,作为存储元的条件: 有两个稳定状态。即可以存储“0”、“1” 。 在外界的激励下,能够进入要求的状态。即可以写入“0”、“1”。 能够识别器件当前的状态。即可以读出所存的“0”、“1”。,2019/5/13,20,六管静态RAM基本存储元电路,2019/5/13,21,单管DRAM基本存储元电路,2019/5/13,22, 存储单元:由一组存储元件组成,可以同时进行读写。 存储体(存储阵列):把大量存储单元电路按一定形式排列起来,即构成存储体。存储体一般都排列成阵列形式,所以又称存储阵列。 存储单元的地址:存储体中每个存储单元被赋予的一个唯一的编号。存储单元的地址用于区别不同的存储单元。要对某一存储单元进行存取操作,必须首先给出被访问的存储单元的地址

《计算机组成原理 第 4 章 存储器系统(修改版)》由会员206****923分享,可在线阅读,更多相关《计算机组成原理 第 4 章 存储器系统(修改版)》请在金锄头文库上搜索。

人教版小学英语单词分类记忆汇总表excel版

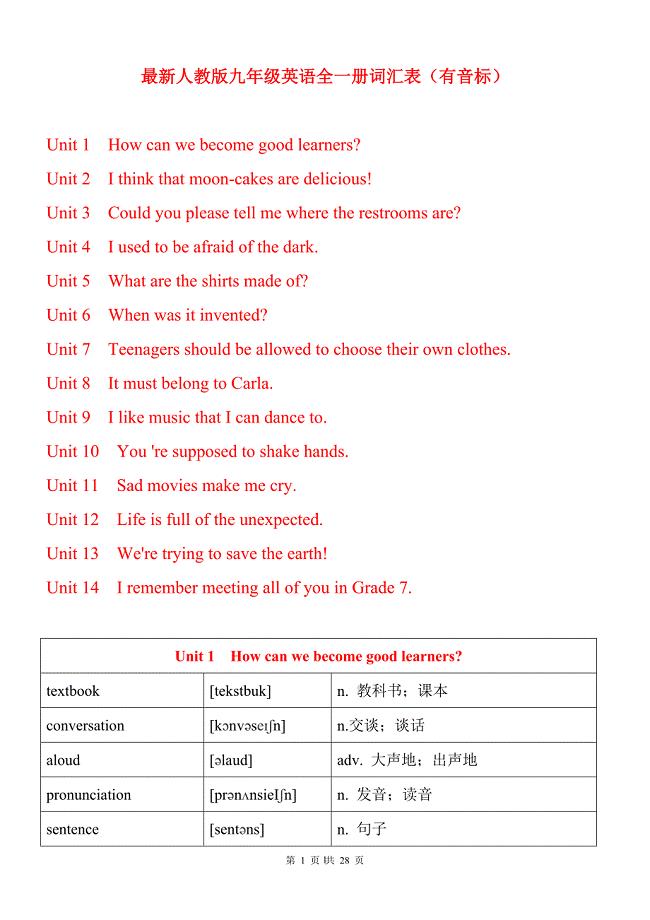

人教版九年级全一册英语词汇

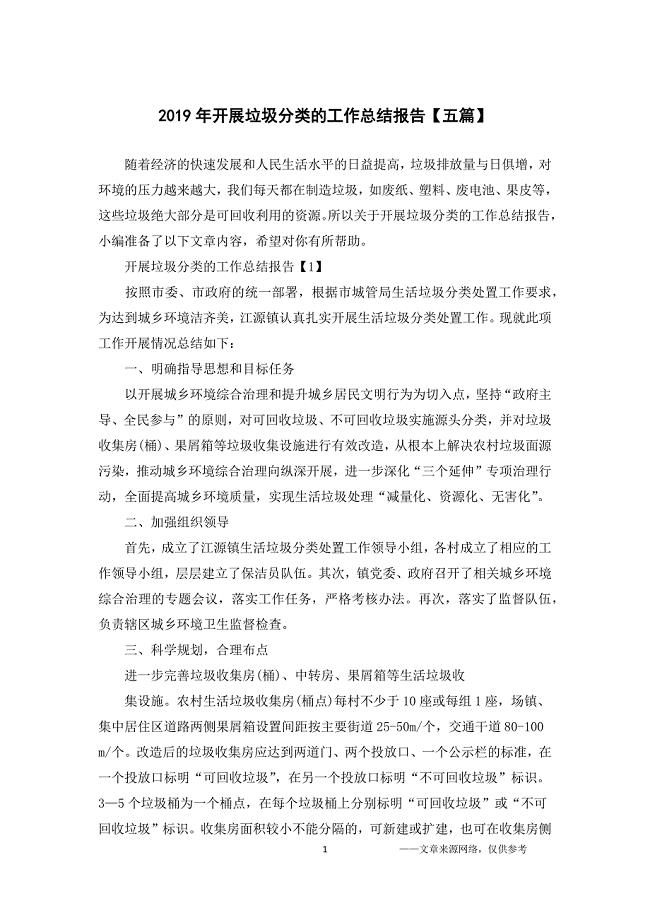

2019年开展垃圾分类的工作总结报告【五篇】

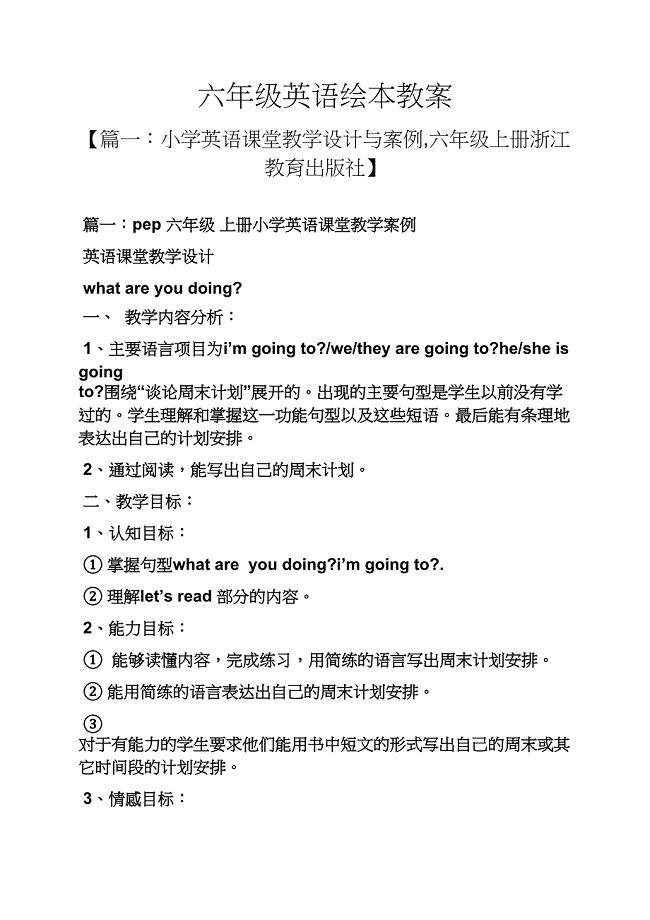

六年级英语绘本教案

外研版小学英语单词表全带音标(一年级起点1-12册)

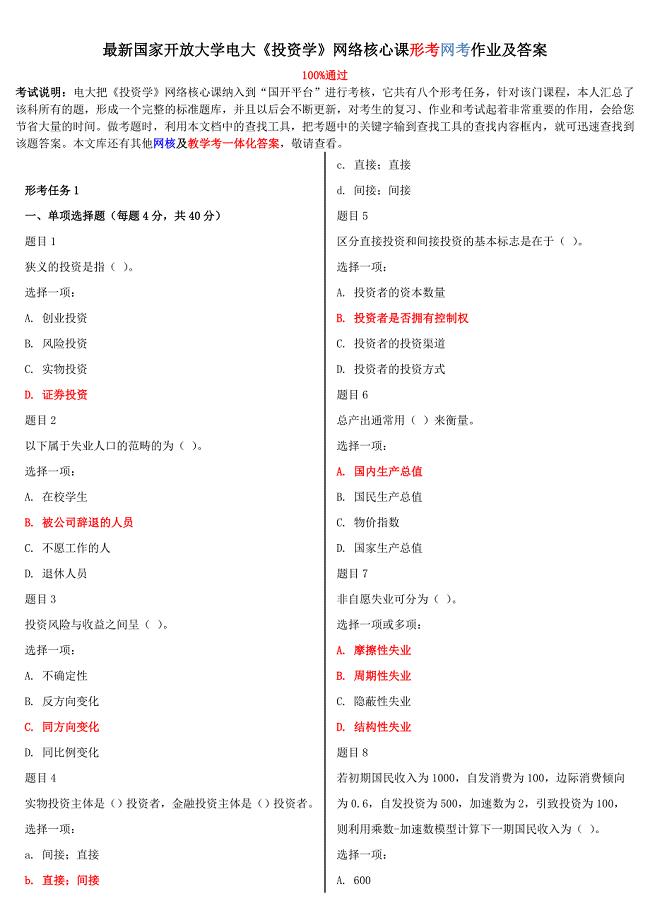

最新国家开放大学电大投资学网络核心课形考网考作业及答案

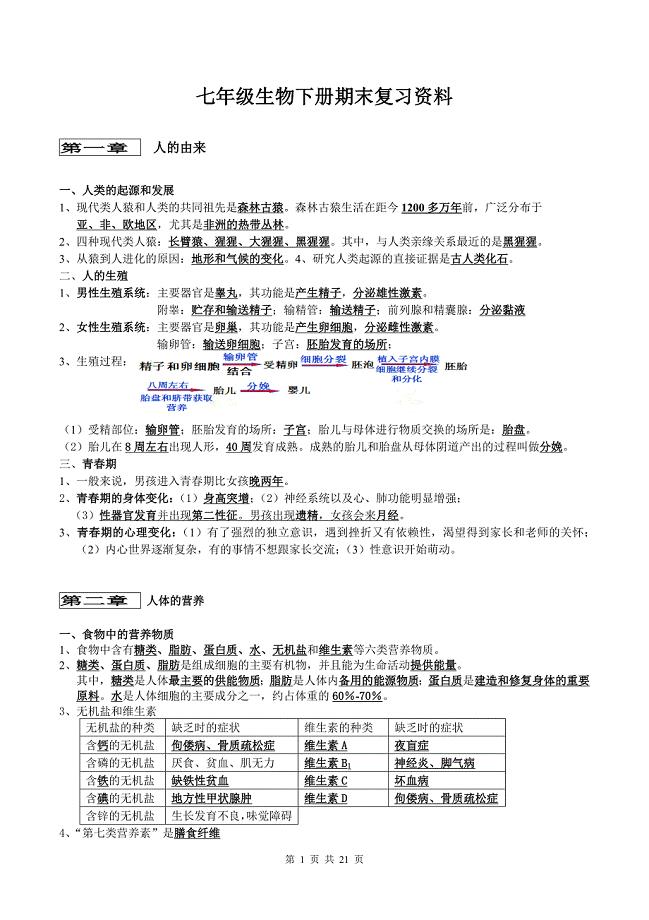

初中人教版七年级下册生物复习提纲

高中英语语法大全高中英语语法系统全解word版

☆初中英语语法专项练习习题以及答案

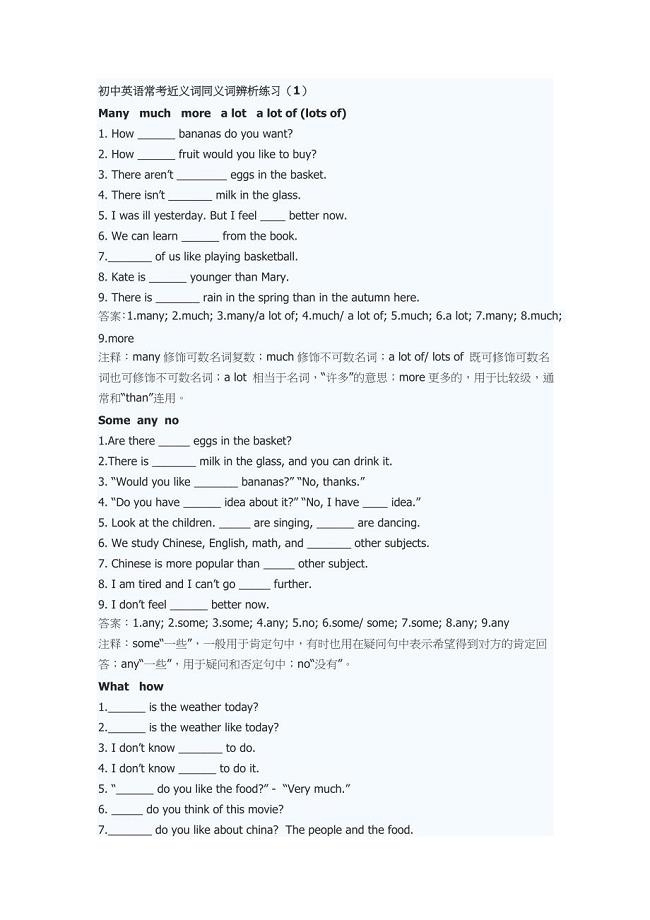

初中英语常考近义词同义词辨析

高中物理选修3-5全套教案(人教版) (1)

英语绘本《WeatherReport》教学设计

防护功能平战转换设计专篇各专业

初中人教版七年级上册下册全册生物复习提纲21页 (1)

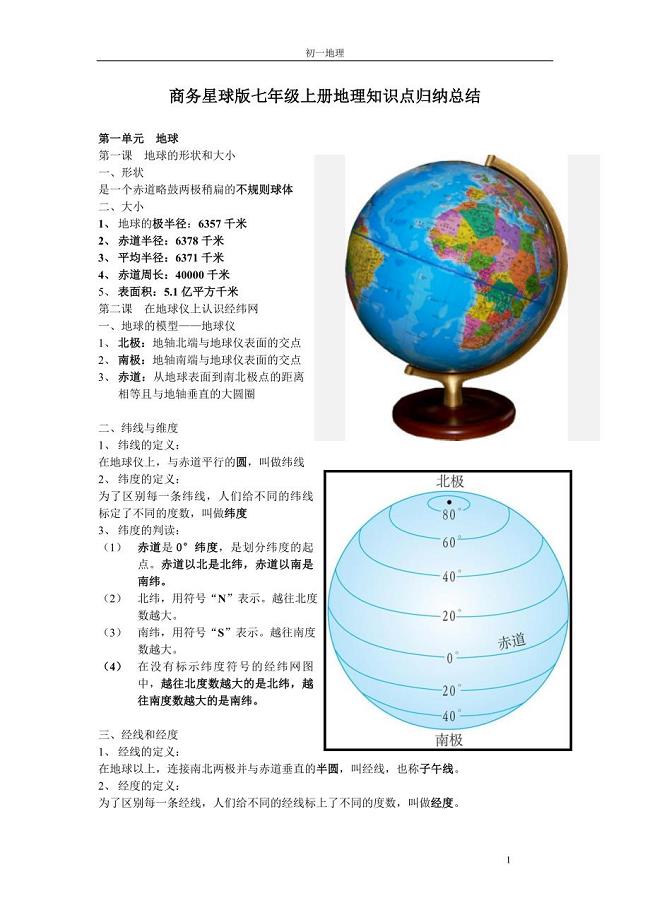

商务星球版七年级上册地理知识点归纳总结

初中人教版七年级上册下册全册生物复习提纲21页 (2)

高中高考语文作文词汇句型优美句子万能语句大全

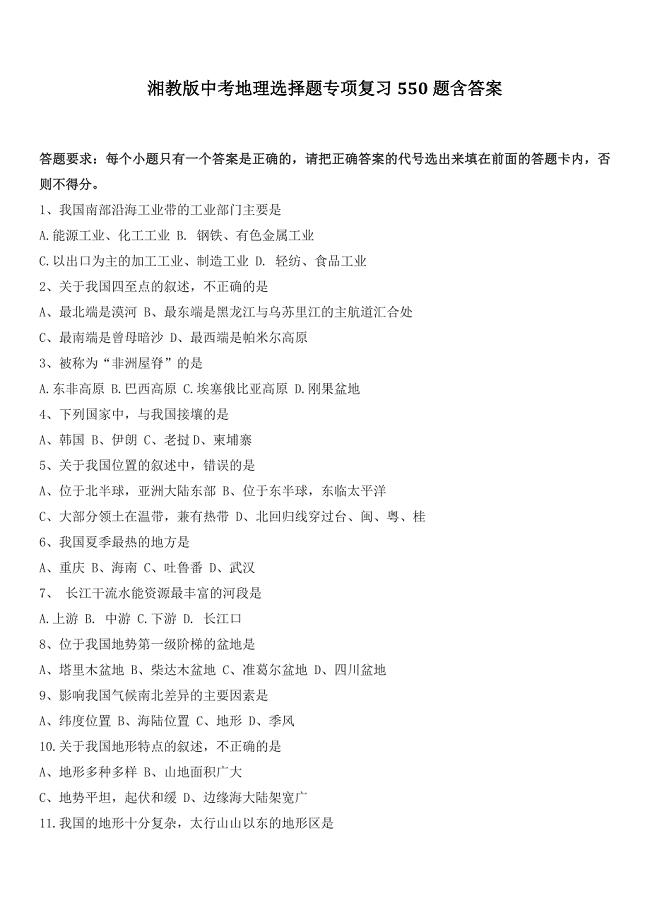

中考地理选择题专项复习550题含答案

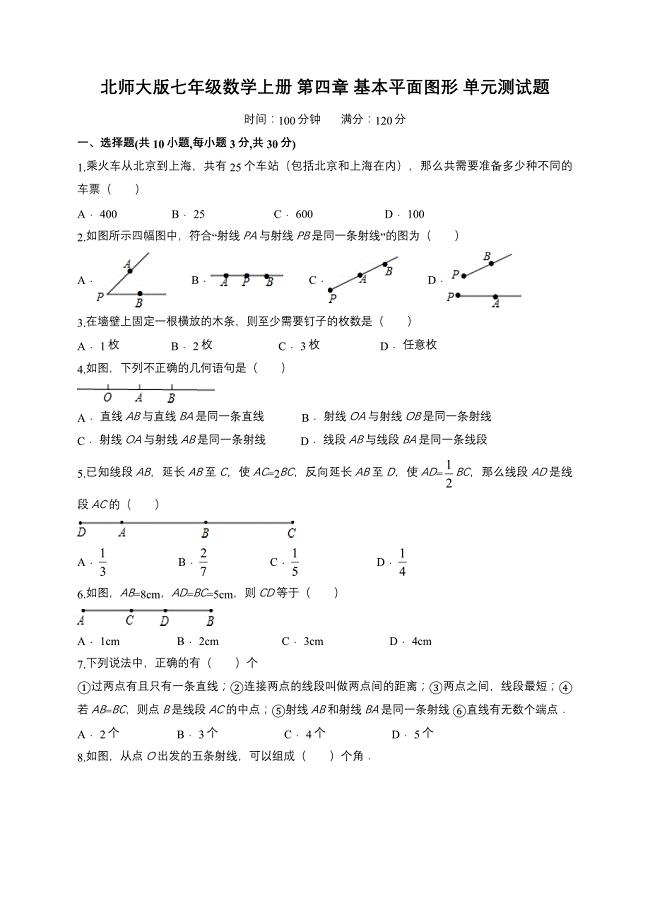

北师大版七年级数学上册第四章基本平面图形单元测试题含解析

人教版七年级数学上册第一章有理数单元检测题解析版

开学第一课安全教育-主题班会教育教学课件

开学第一课安全教育-主题班会教育教学课件

2024-04-09 29页

高中英语元宵节猜灯谜活动英文课件

高中英语元宵节猜灯谜活动英文课件

2024-04-08 25页

部编版高一语文上册(必修一)《“探界者”钟扬》课件

部编版高一语文上册(必修一)《“探界者”钟扬》课件

2024-04-08 13页

部编版高一语文上册(必修一)《读书:目的和前提》课件

部编版高一语文上册(必修一)《读书:目的和前提》课件

2024-04-08 17页

部编版高一语文上册(必修一)《喜看稻菽千重浪——记首届国家最高科技奖获得者袁隆平》课件

部编版高一语文上册(必修一)《喜看稻菽千重浪——记首届国家最高科技奖获得者袁隆平》课件

2024-04-08 17页

部编版高一语文上册(必修一)《立在地球边上放号》课件

部编版高一语文上册(必修一)《立在地球边上放号》课件

2024-04-08 11页

部编版高一语文上册(必修一)《峨日朵雪峰之侧》课件

部编版高一语文上册(必修一)《峨日朵雪峰之侧》课件

2024-04-08 14页

部编版高一语文上册(必修一)《沁园春长沙》课件

部编版高一语文上册(必修一)《沁园春长沙》课件

2024-04-08 17页

部编版高一语文上册(必修一)《拿来主义》课件

部编版高一语文上册(必修一)《拿来主义》课件

2024-04-08 15页

部编版高一语文上册(必修一)《红烛》课件

部编版高一语文上册(必修一)《红烛》课件

2024-04-08 16页