计算机组成原理第三章ppt(page38-45)

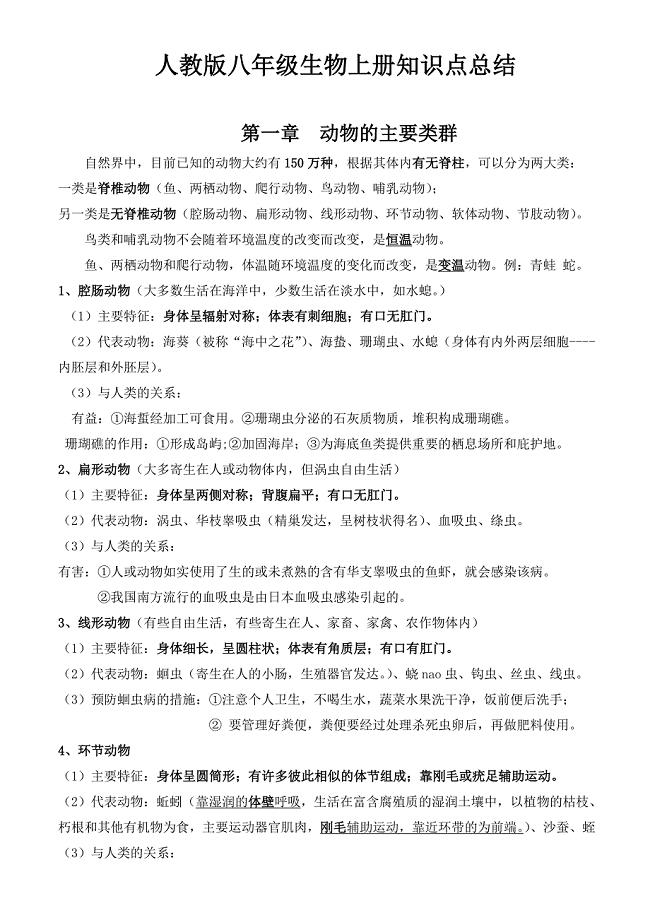

150页1、第三章 存储系统,1、理解存储器的存储原理 2、掌握存储器的扩展方法 3、掌握ROM,闪存,EPROM的特点 4、理解高速存储器的原理、主存的构成 5、掌握DRAM的刷新方法 6、掌握多模块交叉存储器和双端口存储器的特点 7、掌握cache的工作原理、cache与主存的地址变换关系,本章要点,第三章 存储系统,存储器:计算机系统中用来存储程序 、数据的设备。,3.1 存储器概述,一、什么是存储器,1、按存储介质分: 半导体存储器: 利用触发器的双稳态或MOS管栅极有无电荷来 表示二进制的0/1。 磁表面存储器:利用两种不同的剩磁状态表示二进制0/1。常见的有磁带、磁盘两种。 光及磁光存储器: (1)利用激光在非磁性介质上写入和读出信息,也称第一代 光存储(技术)(Optical Memory)。 (2)利用激光在磁记录介质上存储信息,也称第二代光存储技术,二.存储器分类,3.1 存储器概述,2、按存取方式分: 随机存取存储器RAM(Random Access Memory) 顺序存取存储器SAM(Serial Access Memory) 半顺序存储器,二.存储器分类,3.1 存储器概

2、述,按地址码编址,依照给定地址可以随时访问(R/W)任何存储单元,且访问时间与存储单元的物理位置 无关。,随机存取存储器RAM,【 特点】:速度较快,TM为ns级。常用作 cache和主存。,存储器只能按照某种顺序来存取,存取时间和存取单元的物理位置有关.如磁,顺序存取存储器SAM,【 特点】:速度较慢,TM为ns级。常用外存,信息所在地址按控制字编码形式给出,然后以字符、记录形式成块存取。存取时间与信息所在物理位置有关。,半顺序存储器,【 特点】:容量大,寻址较慢,便宜。 如磁盘。,采用多极结构的原因:主存的速度总落后于CPU的需要,主存的容量总落后于软件的需要。,三. 多级存储体系结构,3.1 存储器概述,多级存储结构一般形式,速度接近于CPU,存放部分数据及中间结果,通过减少主存访问而提高系统速度,解决CPU和内存的速度不匹配问题,弥补主存在速度上的不足,解决主存容量不足的问题,有两种描述方式: 字节数表示法(单位有KB,MB,GB,TB) 单元数位数,3.1 存储器概述,四. 主存储器的技术指标,1、存储容量 存储系统能存放二进制位的总量。,举例:如机器字长32位,其存储器容量

3、为4MB,也 表示为1M32,2、存取时间(Memory Access Time) 孤立地考察某一次R/W 操作所需要的时间, 用TA表示。,3.1 存储器概述,四. 主存储器的技术指标,3、存取周期(Memory Circle Time) 连续访存中一次完整的 R/W 操作所需全部时间, 用TM 表示。TMTA。,3.1 存储器概述,四. 主存储器的技术指标,4、带宽Bm 单位时间存取的信息量,通常用bit/s 或B/s表示 Bm=W/TM(位/秒) 其中: W每次R/W 数据的宽度,一般等于内存字长。TM存取周期。,小 结,1.掌握存储器的分级结构 2.掌握存储器的技术指标,3.2 SRAM存储器,本节主要问题: 1.SRAM是如何存储0.1信息的 2.如何把多个信息集合起来构成SRAM存储器芯片 3.CPU如何译码来确定要读写存储器中的哪个单元? 4.SRAM的芯片结构包括什么部分,如何使用?,3.2.1 SRAM的基本存储单元,存储元:指存放一个二进制位(0/1)的电路。 对于SRAM而言,电路为触发器结构。,一、SRAM存储元电路构成,3.2.1 SRAM的基本存储单元,1状

4、态:T1截止,T2导通(A点高电平,B点低电平) 表示“1”。,0状态:T2截止,T1导通(A点低电平,B点高电平) 表示“0”。,二、电路工作原理,3.2.1 SRAM的基本存储单元,写“0”:在I/O线加低电位。,写“1”:在I/O线加高电位。,写入:首先译码选中。,写完成后译码线上高电位信号撤消,电路 进入保持状态。,二、SRAM电路工作原理,读出 首先译码选中,原来存放的“0”或“1”以不同电位值传到I/O线上。读完成后电路进入保持状态。,二、SRAM电路工作原理,(存储)保持状态 当译码信号撤销以后,电路状态不会发生变化。,地址线 数据线 读写控制信号,3.2.2 SRAM的基本逻辑结构,一、基本的SRAM存储器逻辑结构,1.SRAM存储体阵列,mn位的存储矩阵,作用:把CPU给定的地址码转换成驱动对应存储 单元所需字线和位线信号的电路。,【注意】: n位地址可以产生2个信号,控制2 个存储单元,地址译码方式有两种: 单译码方式:适用于小容量 双译码方式:适用于大容量,2.地址译码驱动系统,单译码方式,译码方案:存储体阵列的每一个存储单元由一条字线驱动。,具体结构见下图,单译

《计算机组成原理第三章ppt(page38-45)》由会员206****923分享,可在线阅读,更多相关《计算机组成原理第三章ppt(page38-45)》请在金锄头文库上搜索。

人教版小学英语单词分类记忆汇总表excel版

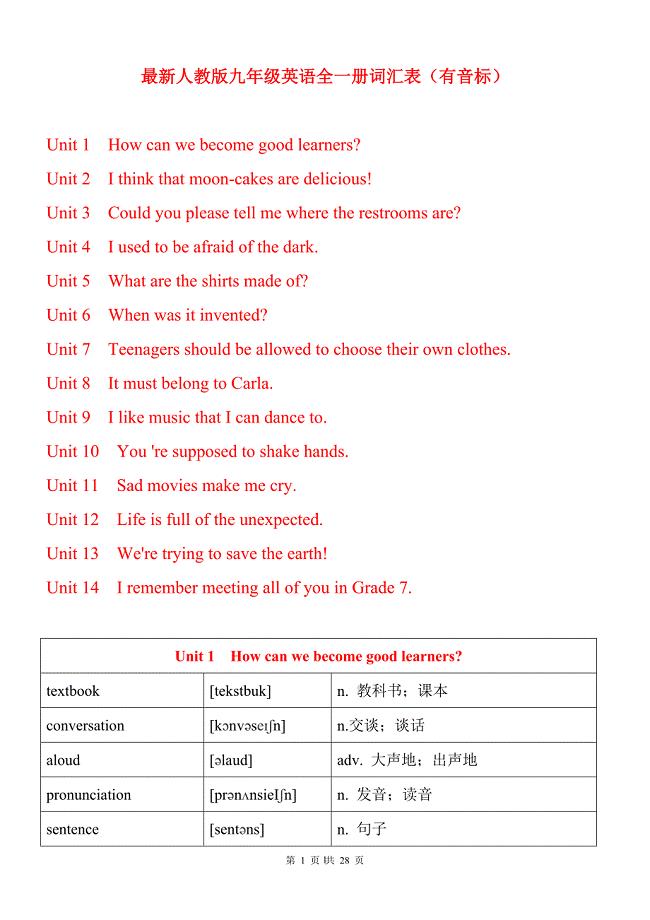

人教版九年级全一册英语词汇

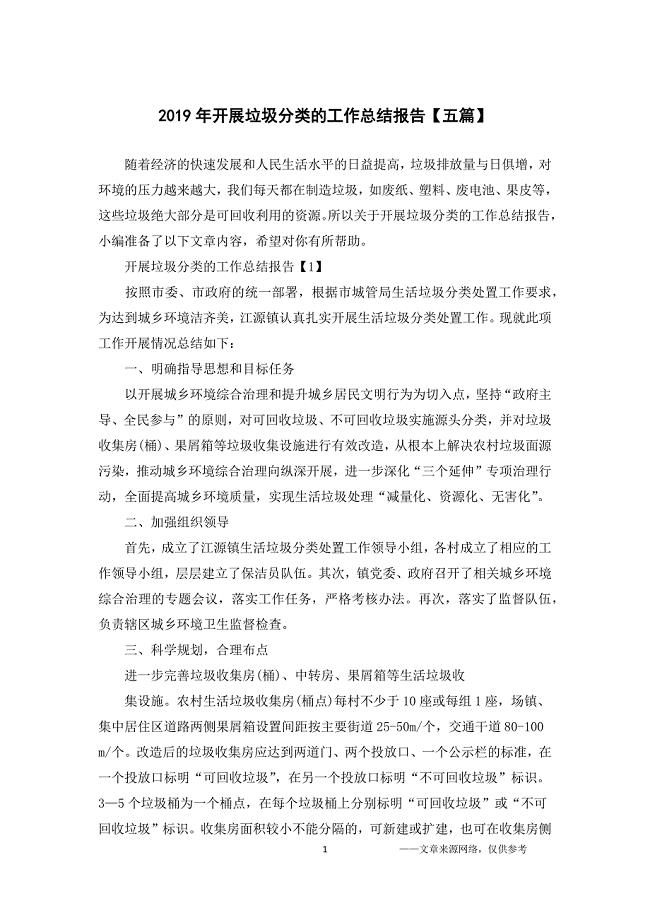

2019年开展垃圾分类的工作总结报告【五篇】

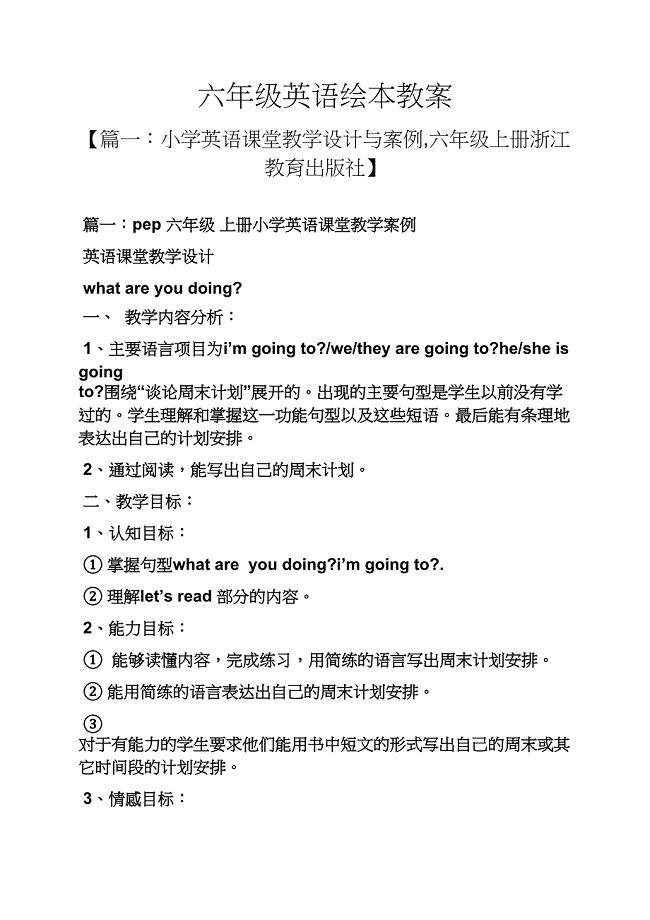

六年级英语绘本教案

外研版小学英语单词表全带音标(一年级起点1-12册)

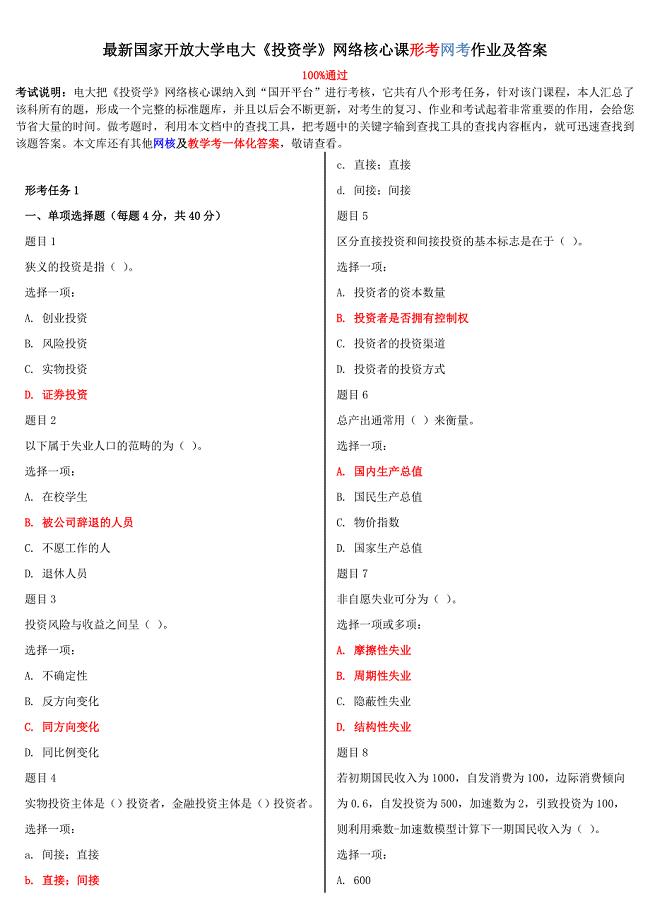

最新国家开放大学电大投资学网络核心课形考网考作业及答案

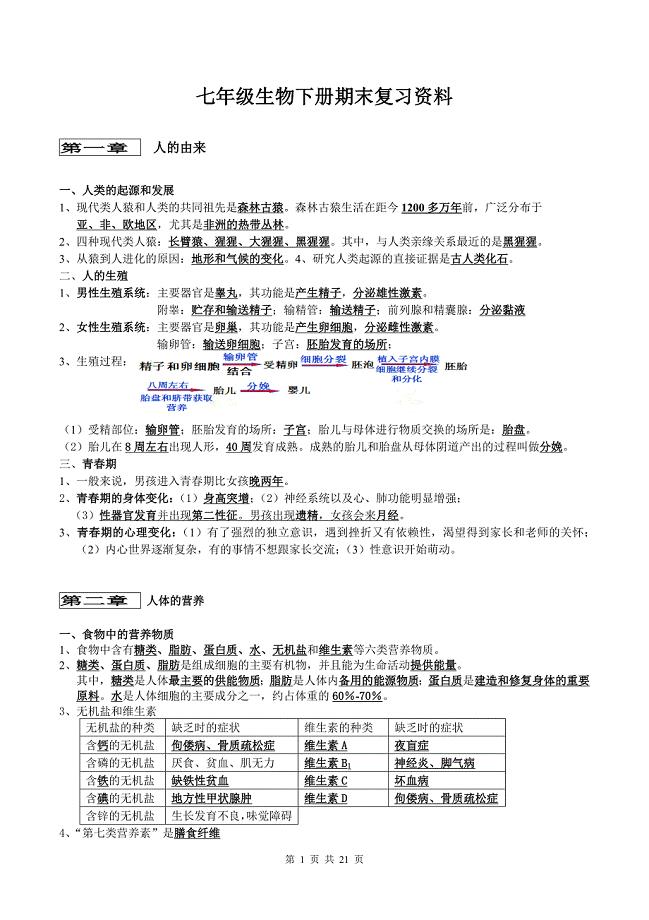

初中人教版七年级下册生物复习提纲

高中英语语法大全高中英语语法系统全解word版

☆初中英语语法专项练习习题以及答案

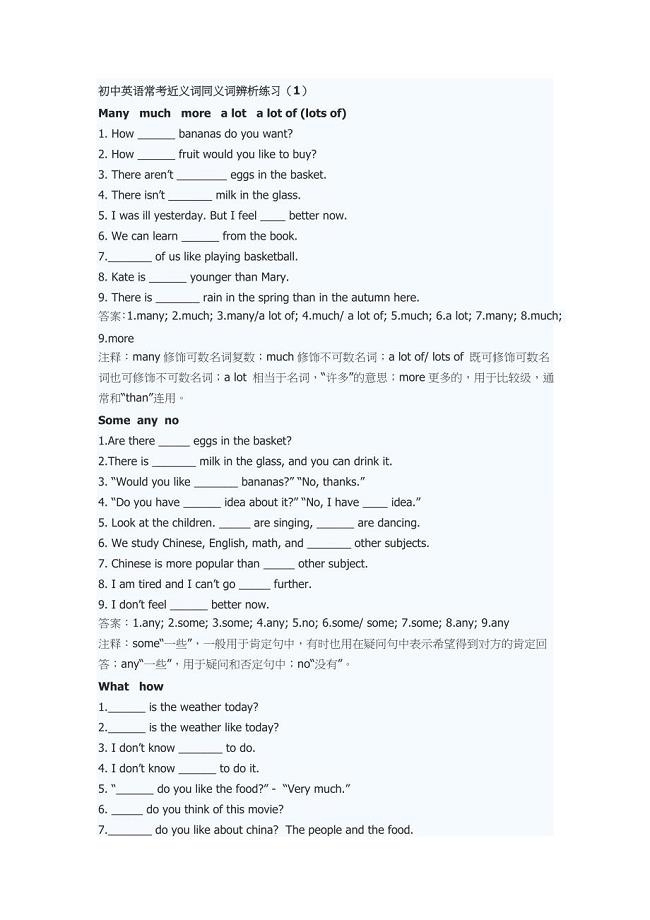

初中英语常考近义词同义词辨析

高中物理选修3-5全套教案(人教版) (1)

英语绘本《WeatherReport》教学设计

防护功能平战转换设计专篇各专业

初中人教版七年级上册下册全册生物复习提纲21页 (1)

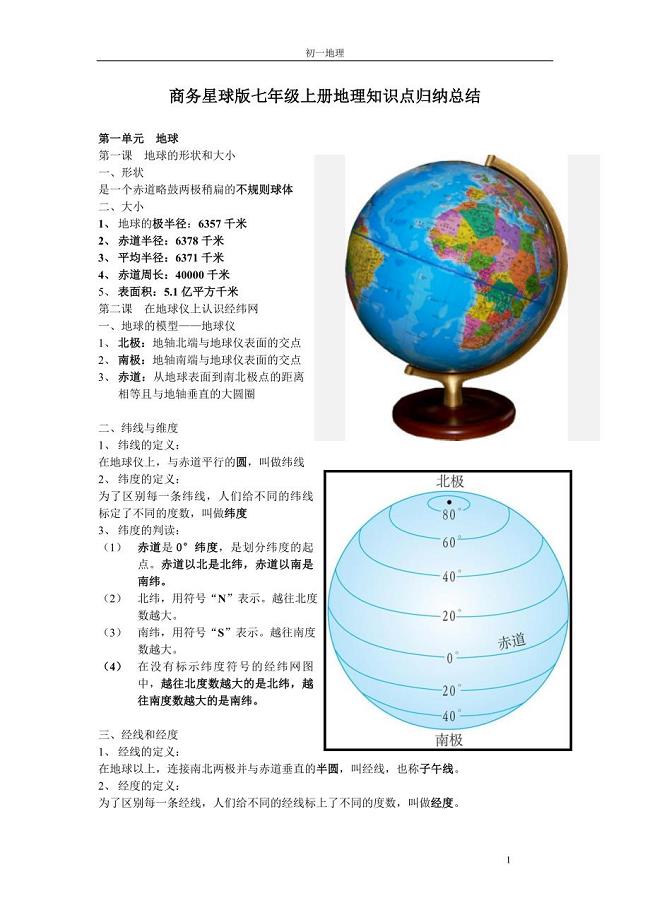

商务星球版七年级上册地理知识点归纳总结

初中人教版七年级上册下册全册生物复习提纲21页 (2)

高中高考语文作文词汇句型优美句子万能语句大全

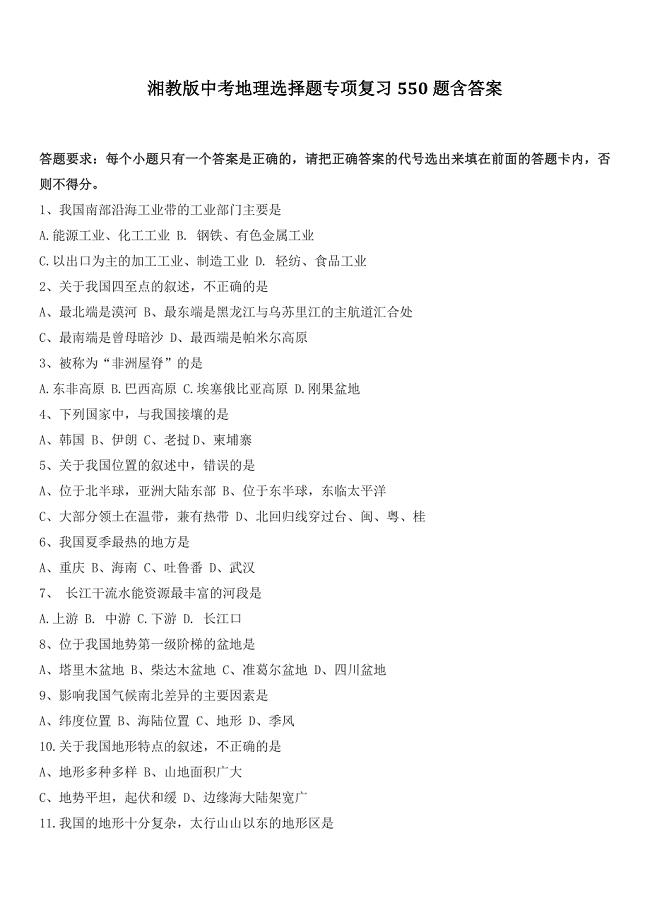

中考地理选择题专项复习550题含答案

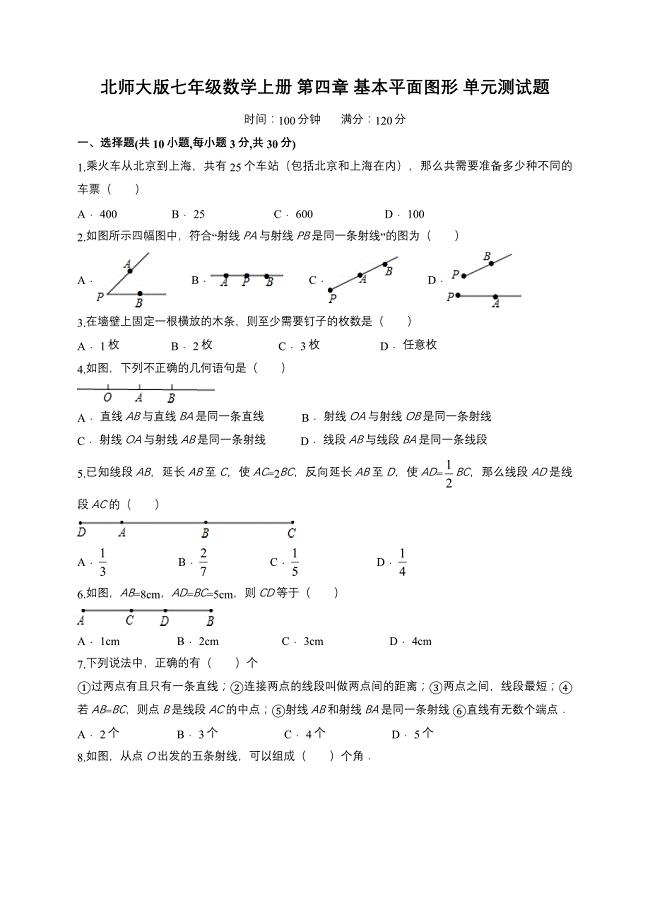

北师大版七年级数学上册第四章基本平面图形单元测试题含解析

人教版七年级数学上册第一章有理数单元检测题解析版

开学第一课安全教育-主题班会教育教学课件

开学第一课安全教育-主题班会教育教学课件

2024-04-09 29页

高中英语元宵节猜灯谜活动英文课件

高中英语元宵节猜灯谜活动英文课件

2024-04-08 25页

部编版高一语文上册(必修一)《“探界者”钟扬》课件

部编版高一语文上册(必修一)《“探界者”钟扬》课件

2024-04-08 13页

部编版高一语文上册(必修一)《读书:目的和前提》课件

部编版高一语文上册(必修一)《读书:目的和前提》课件

2024-04-08 17页

部编版高一语文上册(必修一)《喜看稻菽千重浪——记首届国家最高科技奖获得者袁隆平》课件

部编版高一语文上册(必修一)《喜看稻菽千重浪——记首届国家最高科技奖获得者袁隆平》课件

2024-04-08 17页

部编版高一语文上册(必修一)《立在地球边上放号》课件

部编版高一语文上册(必修一)《立在地球边上放号》课件

2024-04-08 11页

部编版高一语文上册(必修一)《峨日朵雪峰之侧》课件

部编版高一语文上册(必修一)《峨日朵雪峰之侧》课件

2024-04-08 14页

部编版高一语文上册(必修一)《沁园春长沙》课件

部编版高一语文上册(必修一)《沁园春长沙》课件

2024-04-08 17页

部编版高一语文上册(必修一)《拿来主义》课件

部编版高一语文上册(必修一)《拿来主义》课件

2024-04-08 15页

部编版高一语文上册(必修一)《红烛》课件

部编版高一语文上册(必修一)《红烛》课件

2024-04-08 16页