计算机组成原理-存储系统

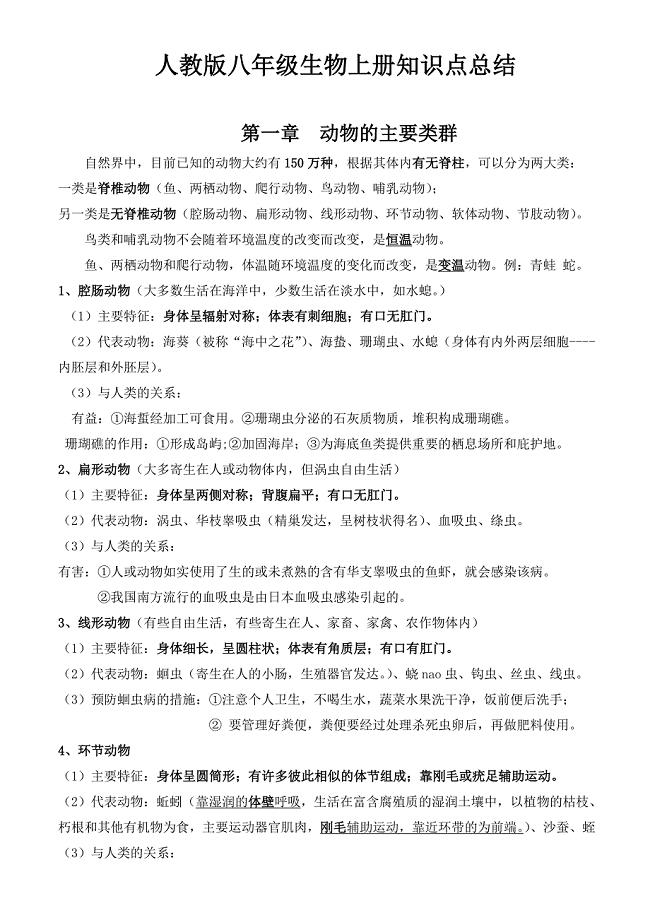

81页1、第四章 存储系统,存储器的两大功能: 1、 存储(写入Write) 2、 取出(读出Read) 三项基本要求: 1、大容量 2、高速度 3、低成本,4.1 概述,4.1.1 存储器相关特性 1.存取时间 从存储器收到读(或写)申请命令,到从存储器读(或写入)信息所需的时间称为存取时间(存储器访问时间) 2.存取周期 存取周期指示存储器做连续访问操作过程中一次完整的存取操作所需的全部时间。 指本次存取开始到下一次存取开始之间所需的时间。即 存取时间加上一段附加时间。,4.1.1 存储器相关特性,3.数据传输率 数据传输率是数据传入或传出存储器的速率。 R 单位:位数/每秒(bps),4.1.2 存储器的分类,1.按存储器在系统中的作用分类 (1)主存(内存) 主要存放CPU当前使用的程序和数据。,速度快,容量有限,(2)辅存,(外存),存放大量的后备程序和数据。,速度较慢,容量大,(3)高速缓存,存放CPU在当前一小段时间内 多次使用的程序和数据。,速度很快,容量小,4.1.2 存储器的分类,2. 按存储介质分类,(1)半导体存储器,利用双稳态触发器存储信息,静态存储器:,依靠电容存储电

2、荷的原理存储信息,(2)磁表面存储器,动态存储器:,容量大,,长期保存信息,,利用磁层上不同方向的磁化区域表示信息。,非破坏性读出,,作外存。,功耗较大,速度快,作Cache。,功耗较小,容量大,速度较快,作主存。,4.1.2 存储器的分类,(3)光盘存储器,速度慢。,利用光斑的有无表示信息。,容量很大,,非破坏性读出,,长期保存信息,,作外存。,3.按存取方式分类,随机存取:,可按地址访问存储器中的任一单元,,(1)随机存取存储器,访问时间与单元地址无关。,4.1.2 存储器的分类,RAM,存取周期或读/写周期,固存:,(ns),:可读可写,ROM,:只读不写,PROM:,用户不能编程,用户可一次编程,EPROM:,用户可多次编程,(紫外线擦除),EEPROM:,用户可多次编程,(电擦除),速度指标:,作主存、高速缓存。,4.1.2 存储器的分类,(2)顺序存取存储器(SAM),访问时读/写部件按顺序查找目标地址,访问时间 与数据位置有关。如:磁带,等待操作,平均等待时间,读/写操作,两步操作,速度指标,(ms),数据传输率,(字节/秒),4.1.2 存储器的分类,(3)直接存取存储

3、器(DAM),访问时读/写部件先直接指向一个小区域,再在该区域内顺序查找。访问时间与数据位置有关。如:磁盘,三步操作,定位(寻道)操作,等待(旋转)操作,读/写操作,速度指标,平均定位(平均寻道)时间,平均等待(平均旋转)时间,数据传输率,(ms),(ms),(位/秒),4.1.3 存储系统的层次结构,三级存储体系结构: 高速缓存 主存 外存 1)主存储器:指能由CPU直接编程访问的存储器。存放需要执行的程序和需要处理的数据。也称为内存。 2)外存储器:指用来存放需要联机保存但暂不使用的程序和数据。对主存的补充和后援。位于主机的逻辑范畴之外。简称为外存。 3)高速缓存:存放最近要使用的程序和数据。解决CPU和主存之间的速度匹配。,4.1.3 存储系统的层次结构,1.主存-外存层次,为虚拟存储提供条件。,增大容量。,将主存空间与部分外存空间组成逻辑地址空间;,CPU,Cache,主存,外存,用户使用逻辑地址空间编程;,操作系统进行有关程序调度、存储空间分配、地址转换等工作。,4.1.3 存储系统的层次结构,2.主存-高速缓存层次 提高速度。,命中,不命中,4.2 半导体存储单元与存储芯片

4、,工艺,双极型,MOS型,TTL型,ECL型,速度很快、,功耗大、,容量小,电路结构,PMOS,NMOS,CMOS,功耗小、,容量大,工作方式,静态MOS,动态MOS,(静态MOS除外),存储信息原理,静态存储器SRAM,动态存储器DRAM,(双极型、静态MOS型):,依靠双稳态电路内部交叉反馈的机制存储信息。,(动态MOS型):,依靠电容存储电荷的原理存储信息。,功耗较大,速度快,作Cache。,功耗较小,容量大,速度较快,作主存。,4.2.1 双极型存储单元与芯片,基本逻辑电路,1. 二极管:,2. 肖特基二极管:,3. 三极管:,三极管相当于一个由基极控制的无触点开关。当基极和发射极之间的电压差较大时,三极管通导,集电极和发射极电压基本相同。,4.2.1 双极型存储单元与芯片,1.TTL型存储单元,V1 V2,Z,TTL原理:用两个双射极晶体管交叉反馈,构成双稳态电路。 左图中,V1,V2交叉反馈,构成双稳态电路,发射极接 字线Z,如果字线Z为低电平,可读/写,如果字线Z为高电平, 则数据保持。W和W是位线,数据通过W和W读出或写入。,4.2.1 双极型存储单元与芯片,定义: 当

《计算机组成原理-存储系统》由会员206****923分享,可在线阅读,更多相关《计算机组成原理-存储系统》请在金锄头文库上搜索。

人教版小学英语单词分类记忆汇总表excel版

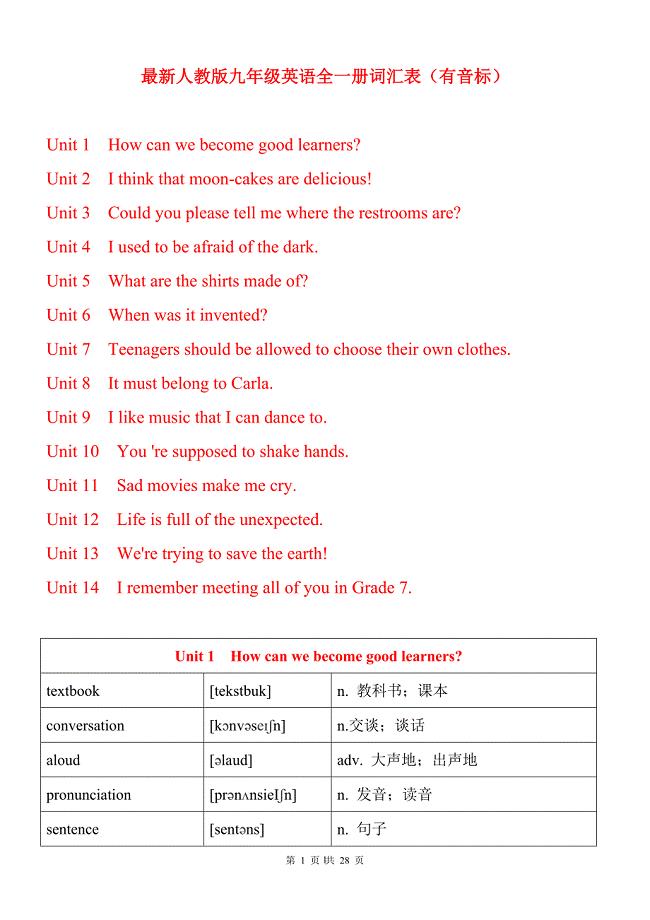

人教版九年级全一册英语词汇

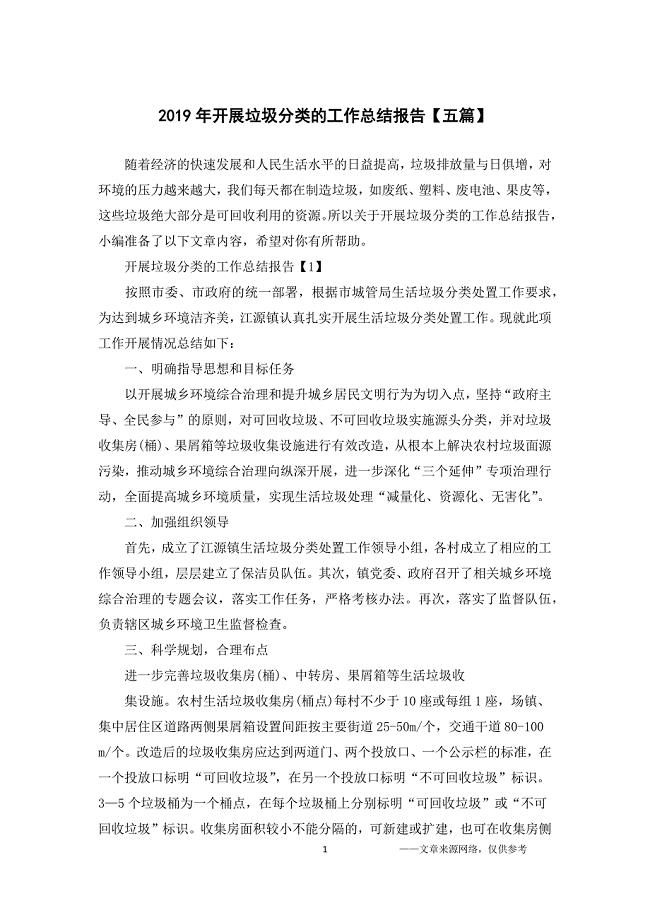

2019年开展垃圾分类的工作总结报告【五篇】

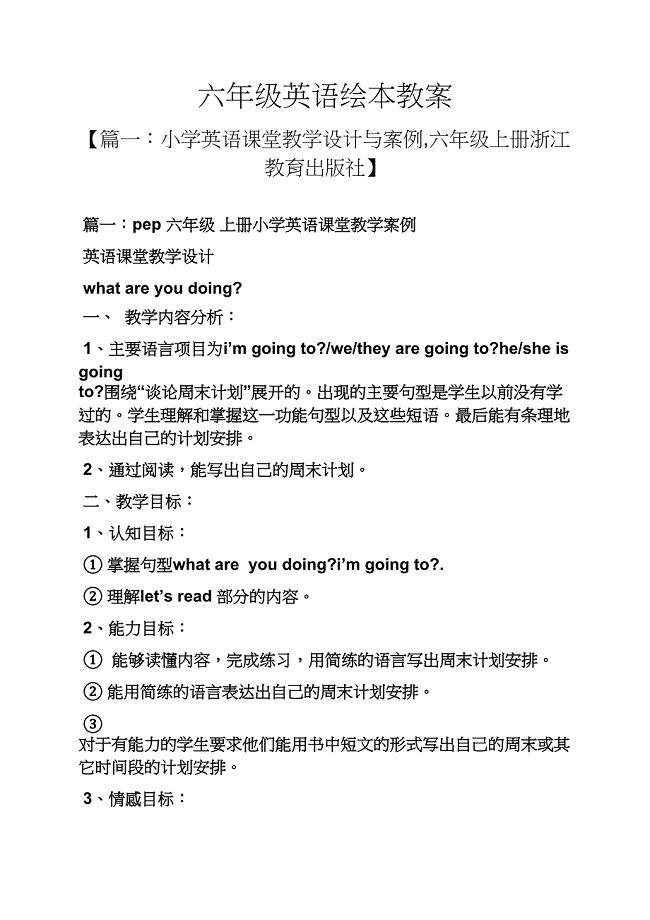

六年级英语绘本教案

外研版小学英语单词表全带音标(一年级起点1-12册)

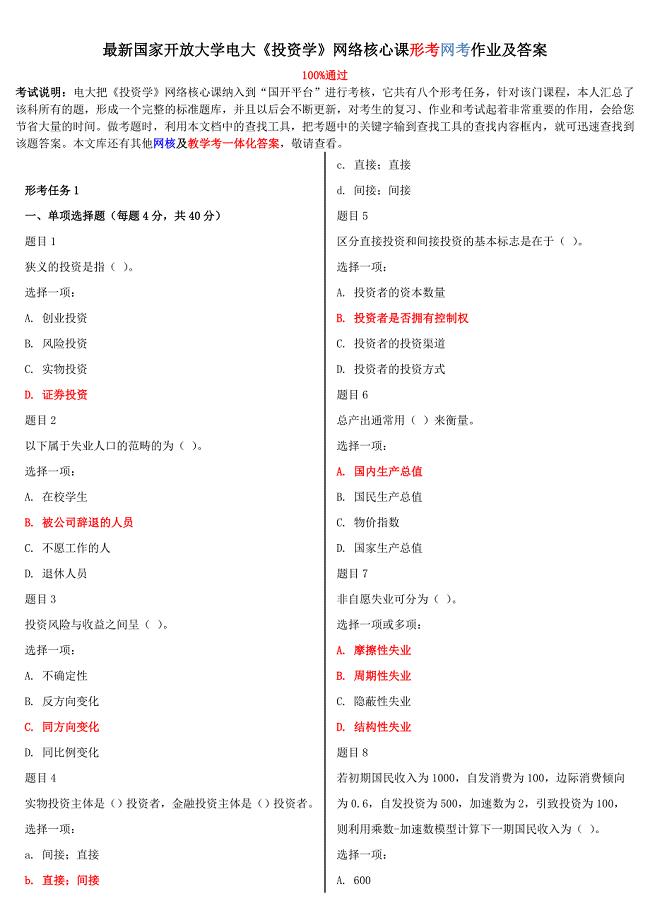

最新国家开放大学电大投资学网络核心课形考网考作业及答案

初中人教版七年级下册生物复习提纲

高中英语语法大全高中英语语法系统全解word版

☆初中英语语法专项练习习题以及答案

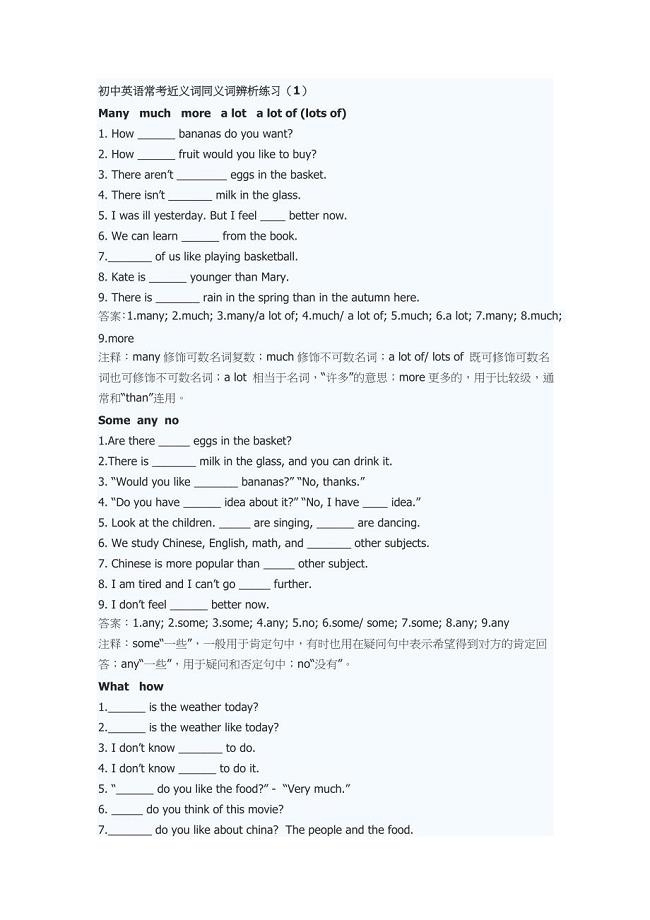

初中英语常考近义词同义词辨析

高中物理选修3-5全套教案(人教版) (1)

英语绘本《WeatherReport》教学设计

防护功能平战转换设计专篇各专业

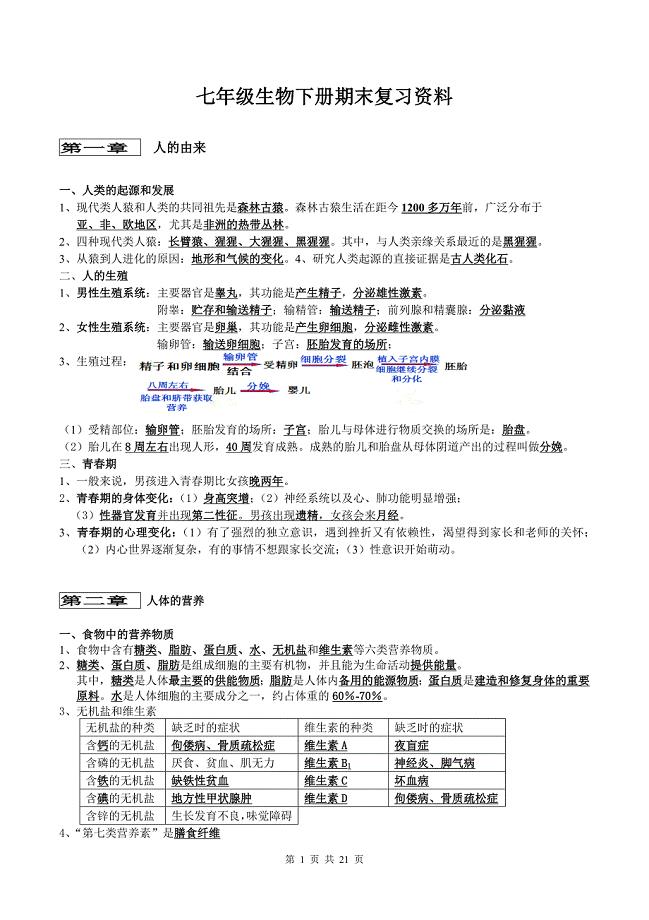

初中人教版七年级上册下册全册生物复习提纲21页 (1)

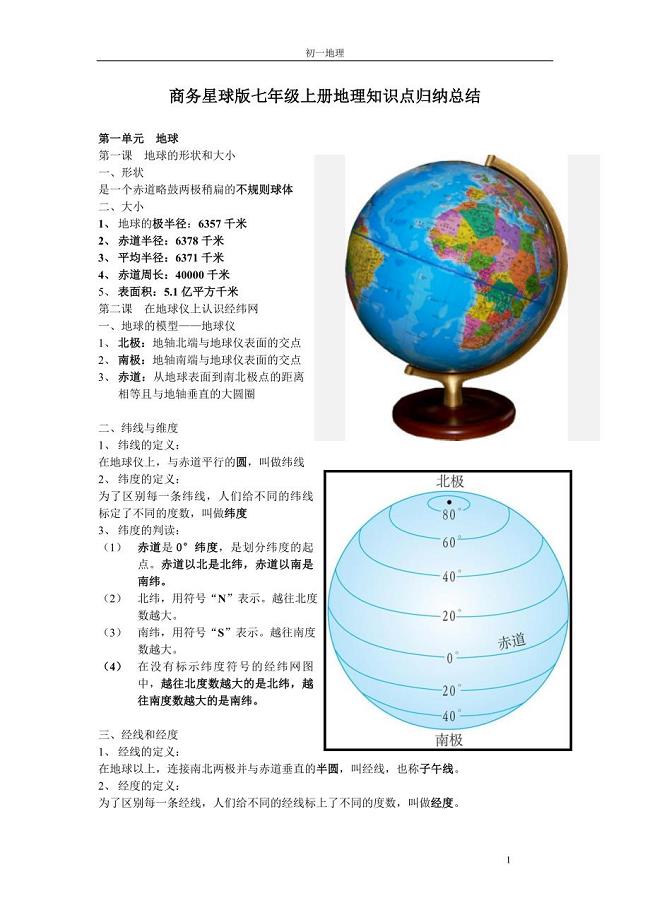

商务星球版七年级上册地理知识点归纳总结

初中人教版七年级上册下册全册生物复习提纲21页 (2)

高中高考语文作文词汇句型优美句子万能语句大全

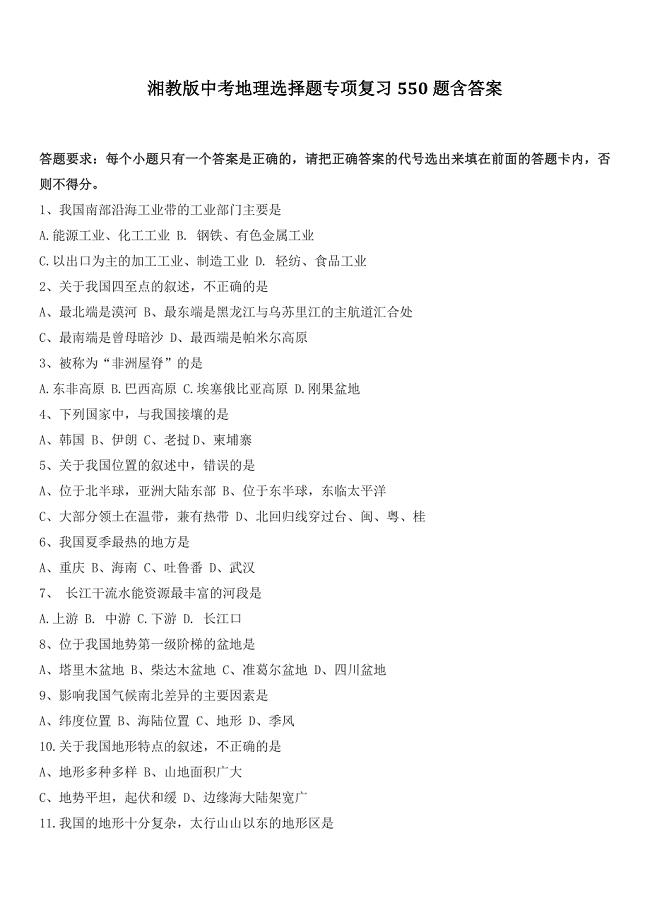

中考地理选择题专项复习550题含答案

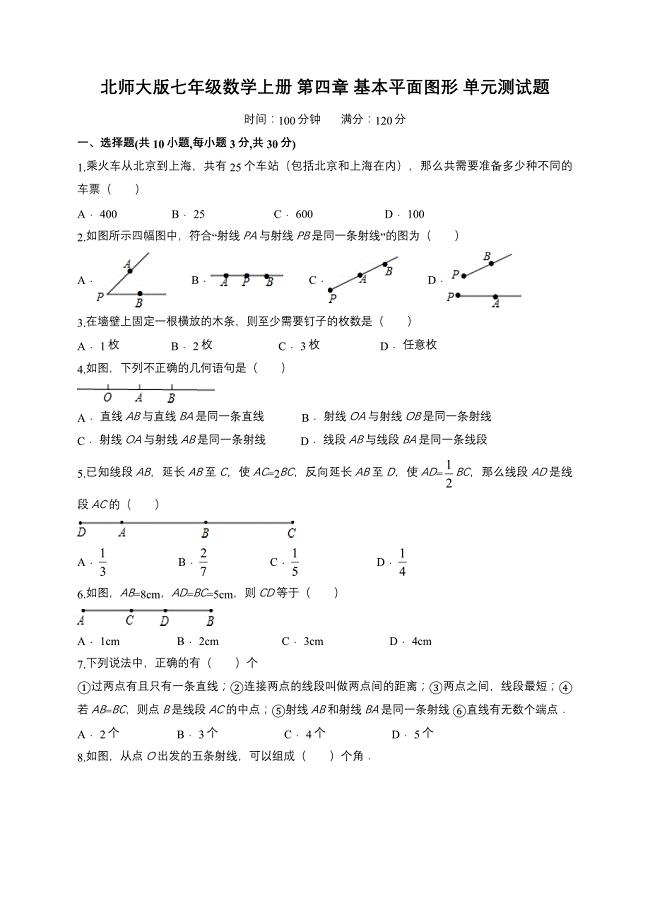

北师大版七年级数学上册第四章基本平面图形单元测试题含解析

人教版七年级数学上册第一章有理数单元检测题解析版

开学第一课安全教育-主题班会教育教学课件

开学第一课安全教育-主题班会教育教学课件

2024-04-09 29页

高中英语元宵节猜灯谜活动英文课件

高中英语元宵节猜灯谜活动英文课件

2024-04-08 25页

部编版高一语文上册(必修一)《“探界者”钟扬》课件

部编版高一语文上册(必修一)《“探界者”钟扬》课件

2024-04-08 13页

部编版高一语文上册(必修一)《读书:目的和前提》课件

部编版高一语文上册(必修一)《读书:目的和前提》课件

2024-04-08 17页

部编版高一语文上册(必修一)《喜看稻菽千重浪——记首届国家最高科技奖获得者袁隆平》课件

部编版高一语文上册(必修一)《喜看稻菽千重浪——记首届国家最高科技奖获得者袁隆平》课件

2024-04-08 17页

部编版高一语文上册(必修一)《立在地球边上放号》课件

部编版高一语文上册(必修一)《立在地球边上放号》课件

2024-04-08 11页

部编版高一语文上册(必修一)《峨日朵雪峰之侧》课件

部编版高一语文上册(必修一)《峨日朵雪峰之侧》课件

2024-04-08 14页

部编版高一语文上册(必修一)《沁园春长沙》课件

部编版高一语文上册(必修一)《沁园春长沙》课件

2024-04-08 17页

部编版高一语文上册(必修一)《拿来主义》课件

部编版高一语文上册(必修一)《拿来主义》课件

2024-04-08 15页

部编版高一语文上册(必修一)《红烛》课件

部编版高一语文上册(必修一)《红烛》课件

2024-04-08 16页

广东省建筑装饰工程竣工验收技术资料统一用表

广东省建筑装饰工程竣工验收技术资料统一用表 水基防锈剂配方组成比例,防锈原理及配制方法

水基防锈剂配方组成比例,防锈原理及配制方法 辩论赛宁要大城市一张床,宁要小城镇一间房

辩论赛宁要大城市一张床,宁要小城镇一间房 【2018年整理】动力气象吕美仲课后答案.pdf

【2018年整理】动力气象吕美仲课后答案.pdf 红楼梦后28回(癸酉本)

红楼梦后28回(癸酉本) 金锄头网企业认证授权书(负责人非法人必须提供)

金锄头网企业认证授权书(负责人非法人必须提供) 服装设计助理实习周记

服装设计助理实习周记 制造机械项目投资分析报告(总投资15000万元)(78亩)

制造机械项目投资分析报告(总投资15000万元)(78亩) 计算机网络技术基础 教学课件 作者 阚宝朋 课件 第2章 网络体系结构与网络协议

计算机网络技术基础 教学课件 作者 阚宝朋 课件 第2章 网络体系结构与网络协议 计算机网络技术基础 教学课件 作者 阚宝朋 课件 第5章 网络层与网络互联

计算机网络技术基础 教学课件 作者 阚宝朋 课件 第5章 网络层与网络互联 计算机网络技术基础 教学课件 作者 阚宝朋 课件 第1章 网络基础知识

计算机网络技术基础 教学课件 作者 阚宝朋 课件 第1章 网络基础知识 输煤管道生产建设项目可行性研究报告

输煤管道生产建设项目可行性研究报告