SOPC实验报告

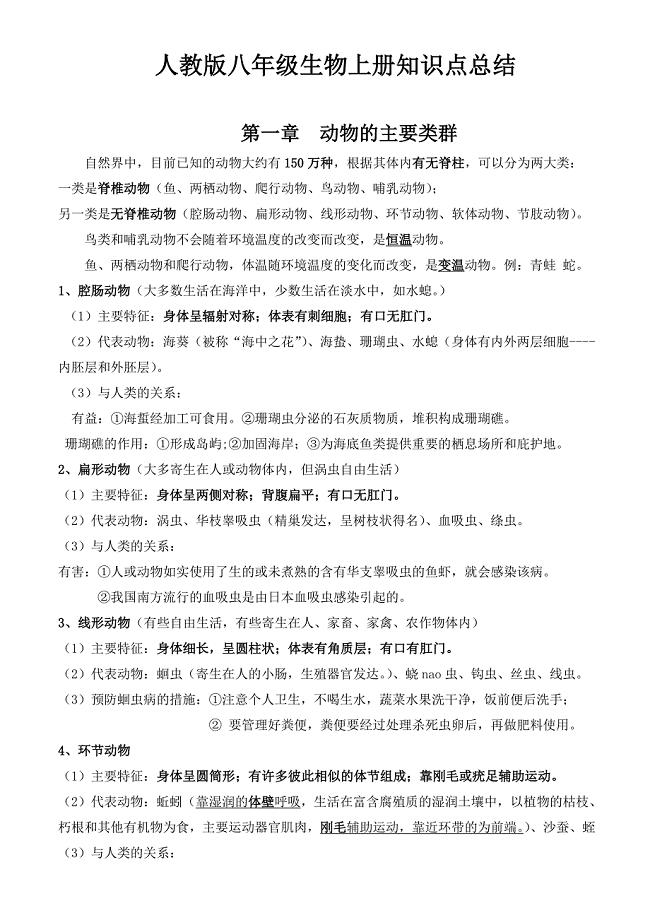

19页1、 SOPC系统设计技术实验报告姓 名: 学 号: 院 系: 信息科学与工程学院专 业:电子科学与技术指导老师: 完成日期: 2015年04月25日实验二、NIOSII实现串口收发数据及LCD显示一、实验目的(1)进一步熟悉QuartusII、SOPC Builder、NIOS II IDE的操作;(2)掌握SOPC硬件系统及NIOS II软件的开发流程。二、实验内容(1)、实验平台:硬件:PC级、SmartSOPC+教学实验开发平台;软件:Quartus II 9.0, SOPC Builder 9.0, NIOS II IDE 9.0。(2)、实验内容:建立包含SDRAM、JTAG_UART、Timer、LCD的NIOS II处理器系统,通过JTAG_UART从IDE的控制端窗口读取输入值N,计算1至N的累加值,并将计算结果及计算花费时间的显示在LCD中。三、实验步骤3.1硬件设计根据实验内容,可以得出本次实验的硬件结构图如图3.1所示:图3.1 硬件设计结构图具体硬件设计步骤如下:1)、在Quartus II中建立一个工程命名为:smallCore,器件设置为EP3C55F484C

2、8;2)、以原理图输入方式建立空白顶层模块,并保持;3)、打开SOPC Builder,命名SOPC系统名称为nios2system,开始建立NIOS II系统。4)、双击SOPC Builder主界面左侧中的“Nios II Processor”,出现Nios II CPU的配置向导对话框,如图1.4所示,在这里可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,不使用硬件乘法器及除法器。然后单击Next进入下一步配置;Instruction Cache项中选择2 Kbytes,在Data Cache项中选择512 Bytes,单击Next进行下一步配置;在“Advanced Features”和“MMU and MPU Settings”选项卡中选择默认参数,然后单击Next,到了“JTAG Debug Module”选项卡,如图1.6所示。这里是选择JTAG调试接口,选择默认的模式Level 1,然后单击Next,到了“Custom Instruction”选项卡,也选择默认参数,最后单击Finish完成对Nios II CPU的配置。5)、添加了Nios

3、II CPU内核后,选中Module Name下的cpu_0,单击鼠标右键,在Rename项中可以重命名cpu_0的名称为cpu,并在“Clock Settings”一栏中将clk_0名称改为clk。6)、双击在SOPC Builder主界面左侧中的Bridges and AdaptersMemory MappedAvalon-MM Clock Crossing Bridge,出现Clock Crossing Bridge的配置向导对话框,在“Slave-to-Master FIFO”中的FIFO depth中选择64。单击“finish”退出配置对话框,并重命名clock_crossing_0的名称为clock_crossing。7)、双击在SOPC Builder主界面左侧中的Memories and Memory ControllersSDRAMDDR SDRAM High Performance Controller,出现DDR SDRAM High Performance Controller的配置向导对话框。修改“General Settings”选项卡的参数配置,参数修改

4、如下:Speed grade:8PLL reference clock frequency:85Memory clock frequency:100Local interface clock frequency:full修改“Modify Parameters”: DDR SDRAM控制器参数,参数修改如下:Total Memory interface DQ width:16 Memory vendor:otherColumn address width:98)、修改DDR SDRAM的控制器ddr_sdram_0的名称为ddr_sdram,并在ddr_sdram左侧中取消cpu.instruction_master和cpu.data_master中的实点,选择clock_crossing.m1的实点,将ddr_sdram控制器连接到Clock Crossing Bridge的m1中。9)、双击在SOPC Builder主界面左侧中的Bridges and AdaptersMemory MappedAvalon-MM Pipeline Bridge,出现Pipeline Bridge的

《SOPC实验报告》由会员206****923分享,可在线阅读,更多相关《SOPC实验报告》请在金锄头文库上搜索。

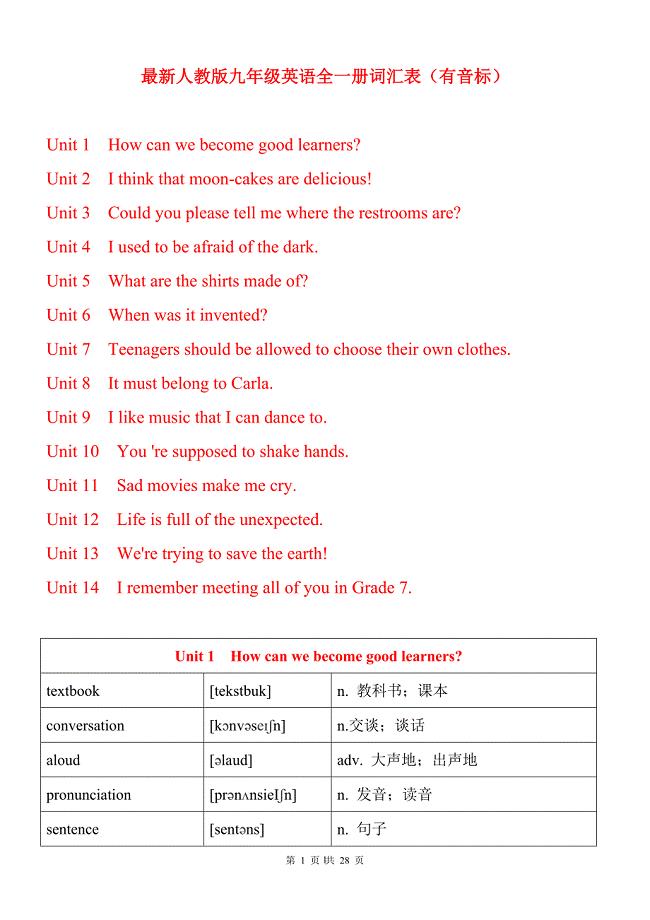

人教版小学英语单词分类记忆汇总表excel版

人教版九年级全一册英语词汇

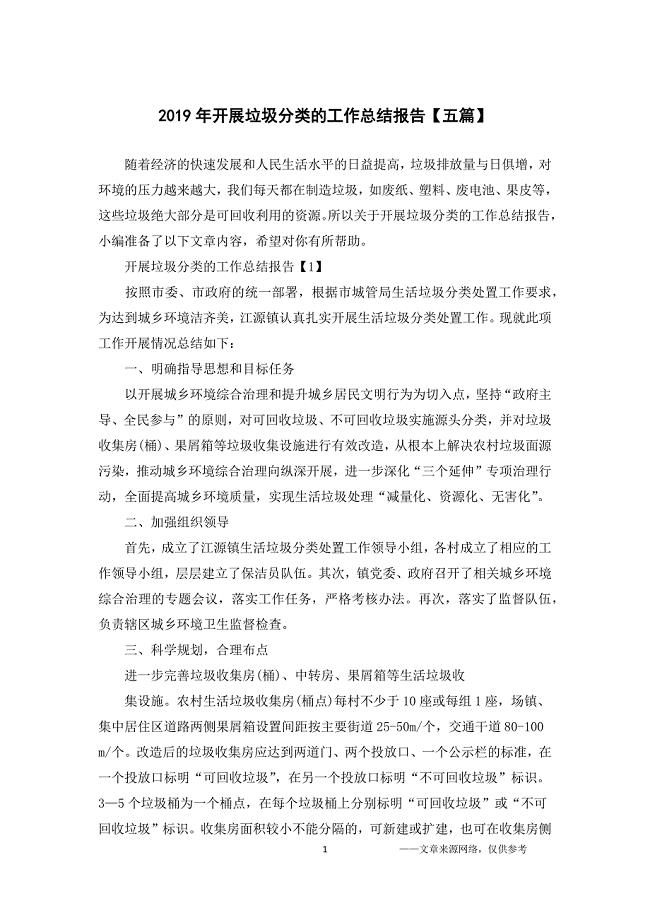

2019年开展垃圾分类的工作总结报告【五篇】

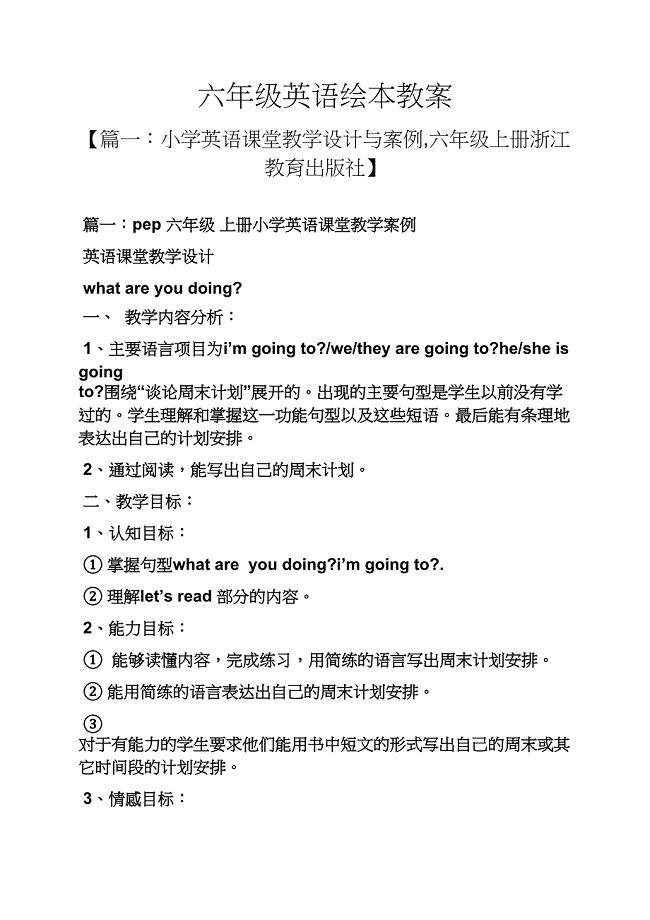

六年级英语绘本教案

外研版小学英语单词表全带音标(一年级起点1-12册)

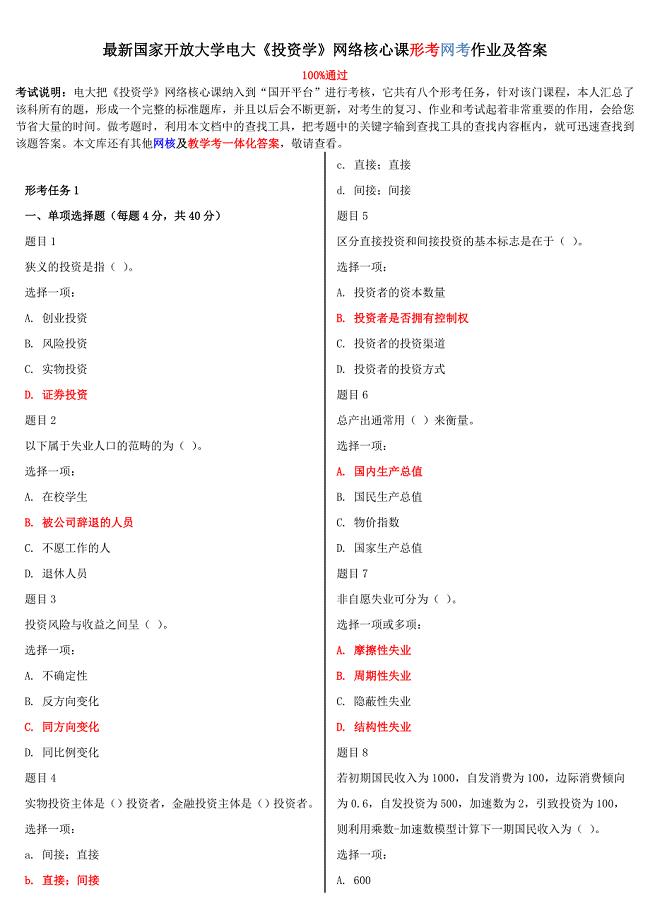

最新国家开放大学电大投资学网络核心课形考网考作业及答案

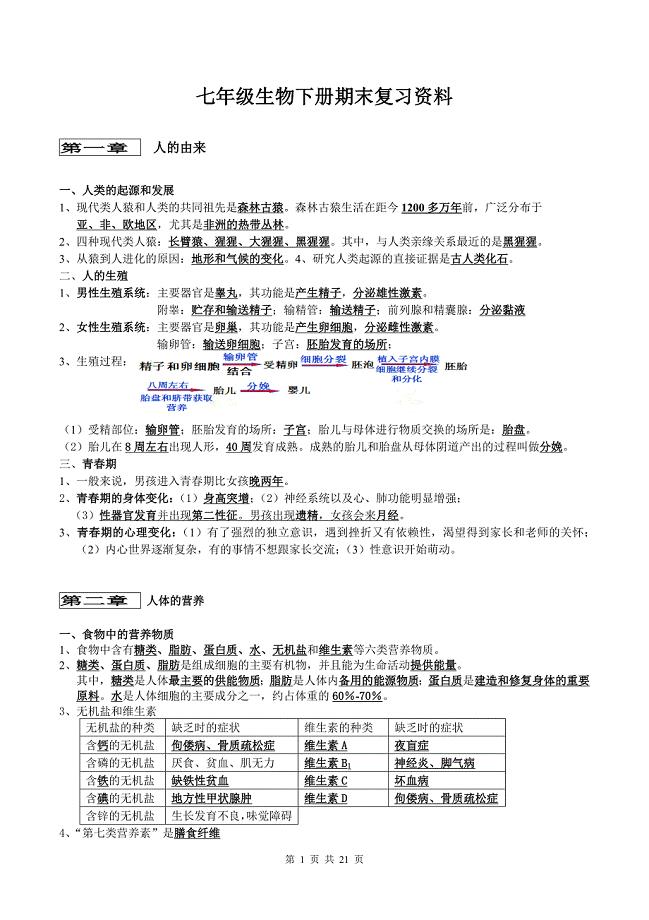

初中人教版七年级下册生物复习提纲

高中英语语法大全高中英语语法系统全解word版

☆初中英语语法专项练习习题以及答案

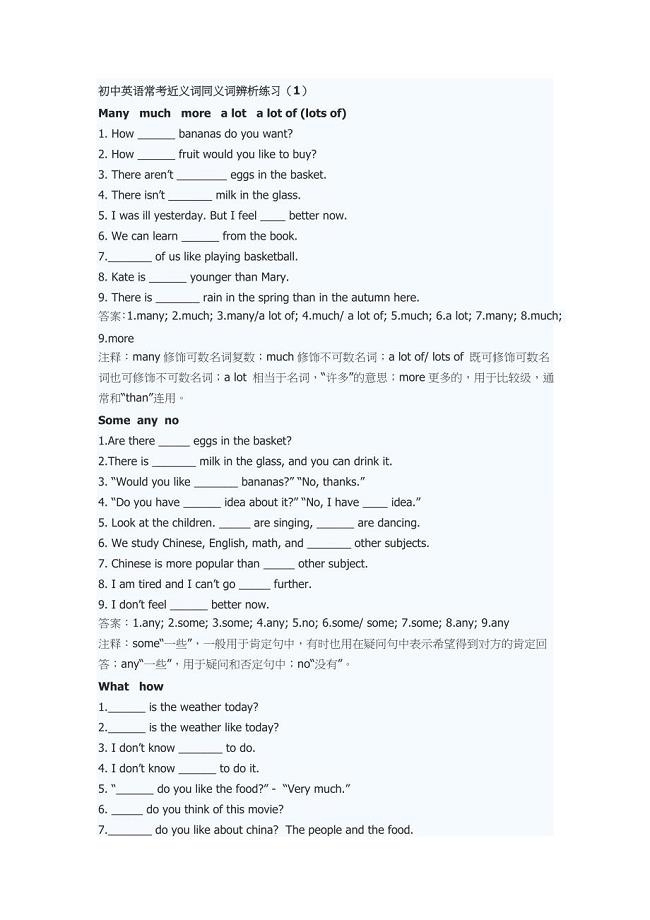

初中英语常考近义词同义词辨析

高中物理选修3-5全套教案(人教版) (1)

英语绘本《WeatherReport》教学设计

防护功能平战转换设计专篇各专业

初中人教版七年级上册下册全册生物复习提纲21页 (1)

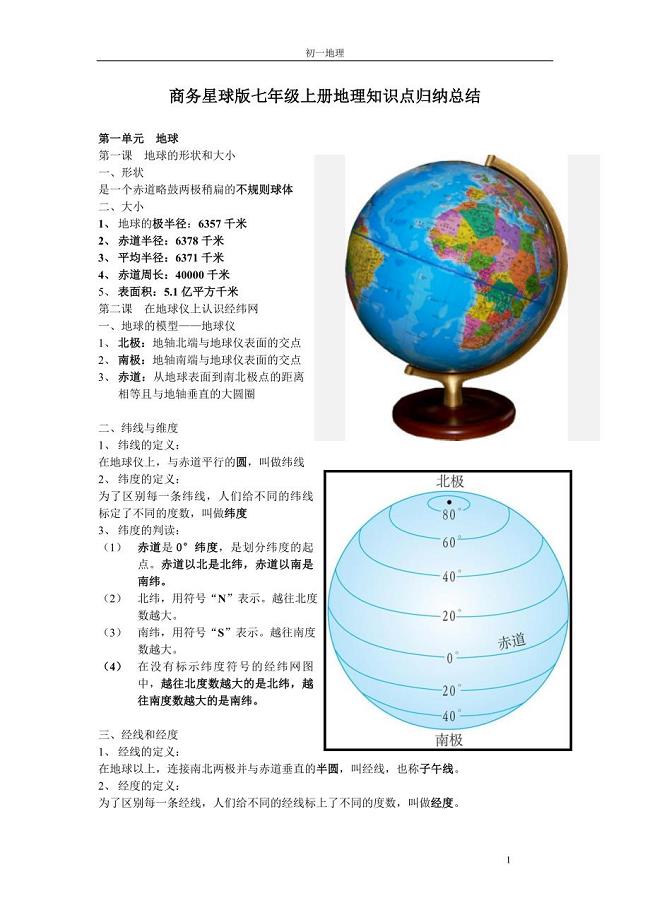

商务星球版七年级上册地理知识点归纳总结

初中人教版七年级上册下册全册生物复习提纲21页 (2)

高中高考语文作文词汇句型优美句子万能语句大全

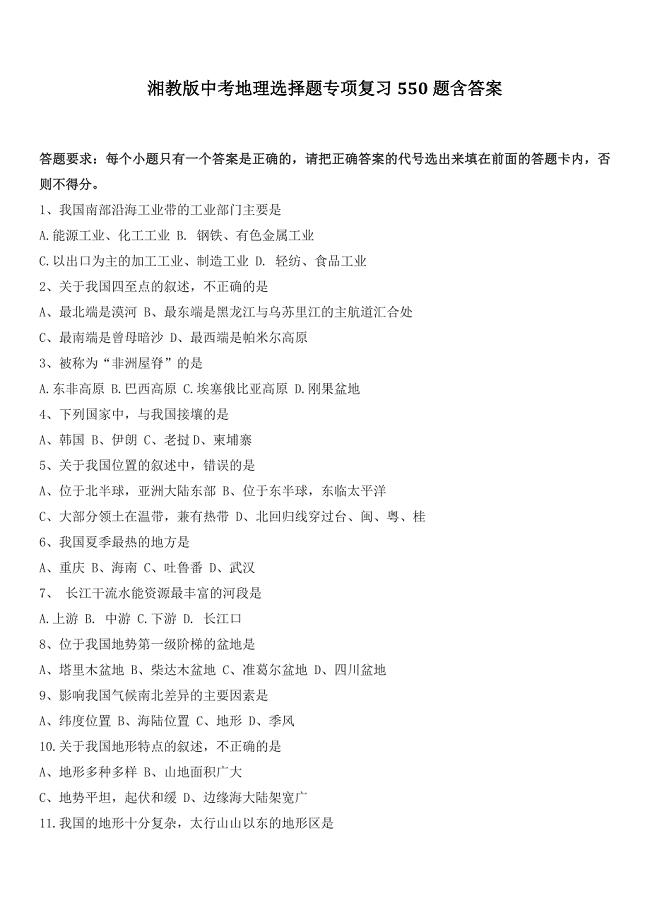

中考地理选择题专项复习550题含答案

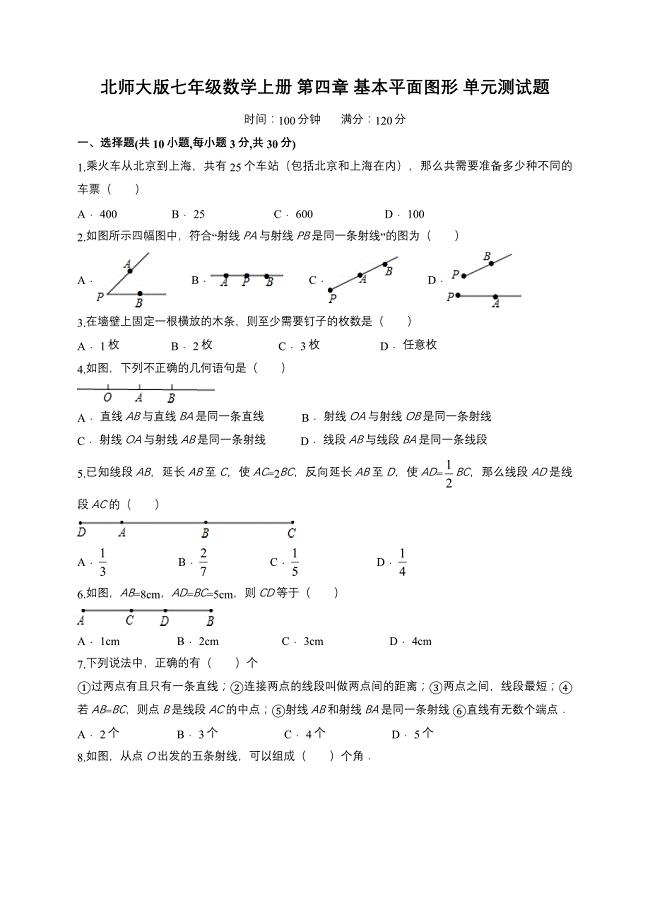

北师大版七年级数学上册第四章基本平面图形单元测试题含解析

人教版七年级数学上册第一章有理数单元检测题解析版

小数数学题:简便计算11道练习题及参考答案A10

小数数学题:简便计算11道练习题及参考答案A10

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A7

小数数学题:简便计算11道练习题及参考答案A7

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A3

小数数学题:简便计算11道练习题及参考答案A3

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A5

小数数学题:简便计算11道练习题及参考答案A5

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A9

小数数学题:简便计算11道练习题及参考答案A9

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A6

小数数学题:简便计算11道练习题及参考答案A6

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A8

小数数学题:简便计算11道练习题及参考答案A8

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A1

小数数学题:简便计算11道练习题及参考答案A1

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A4

小数数学题:简便计算11道练习题及参考答案A4

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A2

小数数学题:简便计算11道练习题及参考答案A2

2024-04-17 2页