常用电平介绍与相互转换

17页1、 1 / 17 常用电平介绍以及相互之间的转换方案 常用电平介绍以及相互之间的转换方案 现在常用的电平有 TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485, LVDS、 GTL、PGTL、CML、HSTL、SSTL 等,这里将对这些电平的特点,使用方法及相互转换方法来学习和讨 论。 1.1. Single-end 电平标准 Single-end 电平标准 常用的单端电平有 TTL, 3.3VLVTTL, 2.5VLVTTL, CMOS, 3.3VLVCMOS, 2.5VLVCMOS, SSTL, 它它 们的电气参数如附表: 電平名稱 Voh Vol Vih Vil Vcc TTL 2.4 0.4 2.0 0.8 5 2.5VLVTTL 2.0 0.2 1.7 0.7 2.5 3.3VVLVTTL 2.4 0.4 2.0 0.8 3.3 CMOS 4.44 0.5 3.5 1.5 5 2.5VLVCMOS 2 0.1 1.7 0.7 2.5 3.3VLVCMOS 2.4 0.5 2.0 0.8 3.3 SSTL 1.82 0.68 1.4

2、3 1.07 2.5 TTL:TTL:Transistor-Transistor Logic 三极管结构 因为 2.4V 与 5V 之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还 会影响速度。所以后来就把一部分“砍”掉了。也就是后面的 LVTTL。 LVTTL 又分 3.3V、2.5V 以及更低电压的 LVTTL(Low Voltage TTL)。 TTL 使用注意:TTL 电平一般过冲都会比较严重,可能在始端串 22 欧或 33 欧电阻; TTL 电平输 入脚悬空时是内部认为是高电平。要下拉的话应用 1k 以下电阻下拉。TTL 输出不能驱动 CMOS 输入。 另外,I/O 為 OC 門時,由於只能吸收大電流而不能向外部提供電流,需要外部上拉或者外部電 源。 CMOS:CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS 2 / 17 . 相对 TTL 有了更大的噪声容限, 输入阻抗远大于 TTL 输入阻抗。 对应 3.3V LVTTL, 出现了 LVCMOS, 可以与 3.3V 的 LVTTL 直接相互驱

3、动。 CMOS 使用注意:CMOS 结构内部寄生有可控硅结构,当输入或输入管脚高于 VCC 一定值(比如一些 芯片是 0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。 ( 1 ) CMOS 电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强 ( 2 )输入端接低内组的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在 1 m A 之内。 ( 3 )当接长信号传输线时,在 CMOS 电路端接匹配电阻。 ( 4 )当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为 R = V 0 / 1 m A . V 0 是 外界电容上的电压。 ( 5 )CMOS 的输入电流超过 1 m A ,就有可能烧坏 CMOS。 T T L 和 CMOS 电路比较: T T L 和 CMOS 电路比较: 1 、T T L 电路是电流控制器件,而 CMOS 电路是电压控制器件。 2 、T T L 电路的速度快,传输延迟时间短( 5 - 1 0 n s ) ,但是功耗大。 CMOS 电路的速度慢,传输延迟时间长( 2 5 - - 5 0 n s ) , 但功耗低。

4、 CMOS 电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。 3 、CMOS 电路的锁定效应: CMOS 电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种 效应就是锁定效应。 当产生锁定效应时, CMOS 的内部电流能达到 4 0 m A 以上,很容易烧毁芯片。 SSTL:SSTL: STUB SERIES TERMINATED LOGIC 短截线串联端接逻辑 3 / 17 SSTL 是专门针对高速内存接口的标准,目前有 SSTL_3(3.3V,DDR), SSTL-2(2.5V,DDR), SSTL-18(1.8V,DDR2), SSTL-15(1.5V,DDR3)几种 Adobe Acrobat 7.0 Document RS232 RS232 : :异步传输标准接口(全双工) RS-232C 逻辑电平定义: 逻辑 1(MARK)=-3V-15V 逻辑 0(SPACE)=+3+15V RS-232-C 总线标准设有 25 条信号线,包括一个主通道和一个辅助通道。 在多数情况下主要使用主通道,对于一般双工通信,仅需几条信号线就

《常用电平介绍与相互转换》由会员第***分享,可在线阅读,更多相关《常用电平介绍与相互转换》请在金锄头文库上搜索。

校园足球汇报

异甘草酸镁注射液【治疗急性药物性肝损伤】Ⅱ期临床研究总结

云教室课程行政伦理学行政良心

语文S版小学二年级语文下册诺亚方舟课件优质课教学课件

未来中考趋势作文考与练

近年来广东历史试题中考易错点分析与教学启示

搜索推广那些事

小学语文二年级上册红领巾真好说课稿设计(说课设计)

新课标人教版二年级语文上册红领巾真好课件

新课程背景下的高中化学课堂教学改革

危机管理与突发事件应对

背影朱自清教案课件二课时

突发公共卫生事件培训

统计学简史及数据科学中南财经大学

水泥混凝土路面技术现状及发展终

有家真好作文讲评课

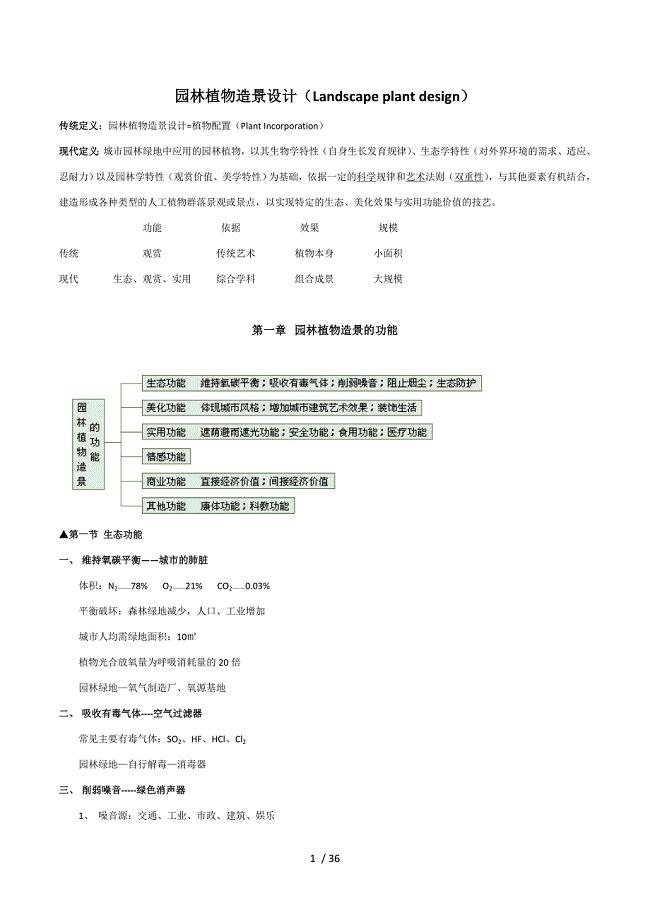

西南大学植物造景设计总复习

海外汉语教学新探索在线交流学习平台Goclef

动态黑色背景年终总结模板

孙子的治军之道与现代管理谋略总结

深入推进“廉洁机关”建设的思路和对策研究

深入推进“廉洁机关”建设的思路和对策研究

2024-04-19 7页

在农村人居环境整治提升工作推进会上的发言

在农村人居环境整治提升工作推进会上的发言

2024-04-19 4页

2024年第二季度党风廉政建设工作要点

2024年第二季度党风廉政建设工作要点

2024-04-19 3页

消防安全集中除患攻坚大整治行动宣传工作方案

消防安全集中除患攻坚大整治行动宣传工作方案

2024-04-19 6页

党纪学习教育党课讲稿:筑牢纪律之基 争当遵规守纪的排头兵

党纪学习教育党课讲稿:筑牢纪律之基 争当遵规守纪的排头兵

2024-04-19 5页

在干部教育培训工作经验分享会上的交流发言

在干部教育培训工作经验分享会上的交流发言

2024-04-19 3页

某县委书记在党纪学习教育专题学习会上的发言

某县委书记在党纪学习教育专题学习会上的发言

2024-04-19 4页

关于切实增强基层党组织政治功能和组织力的调研报告

关于切实增强基层党组织政治功能和组织力的调研报告

2024-04-19 6页

县委书记在党纪学习教育部署会议上的讲话

县委书记在党纪学习教育部署会议上的讲话

2024-04-19 5页

党纪学习教育读书班心得体会

党纪学习教育读书班心得体会

2024-04-19 2页