eda技术实用教程课后答案---潘松-黄继业

19页1、3-3 给出一个 4 选 1 多路选择器的 VHDL 描述。选通控制端有四个输入:S0、S1、S2、S3。当且仅当 S0=0 时:Y=A;S1=0 时:Y=B;S2=0 时:Y=C;S3=0 时:Y=D。 -解:4 选 1 多路选择器 VHDL 程序设计。LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41a ISPORT( A,B,C,D : IN STD_LOGIC;S0,S1,S2,S3 : IN STD_LOGIC;Y : OUT STD_LOGIC);END ENTITY mux41a;ARCHITECTURE one OF mux41a ISSIGNAL S0_3 : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINS0_3xin,y=yin, diff=a, s_out=b);u2: h_suber PORT MAP(x=a, y=sub_in, diff=diff_out,s_out=c);sub_out x0,yin=y0,diff_out=diff0,sub_in=sin,sub_out=a

2、0); u1:f_suber PORT MAP(xin=x1,yin=y1,diff_out=diff1,sub_in=a0,sub_out=a1); u2:f_suber PORT MAP(xin=x2,yin=y2,diff_out=diff2,sub_in=a1,sub_out=a2); u3:f_suber PORT MAP(xin=x3,yin=y3,diff_out=diff3,sub_in=a2,sub_out=a3); u4:f_suber PORT MAP(xin=x4,yin=y4,diff_out=diff4,sub_in=a3,sub_out=a4); u5:f_suber PORT MAP(xin=x5,yin=y5,diff_out=diff5,sub_in=a4,sub_out=a5); u6:f_suber PORT MAP(xin=x6,yin=y6,diff_out=diff6,sub_in=a5,sub_out=a6); u7:f_suber PORT MAP(xin=x7,yin=y7,diff_out=diff7,sub_in=a6,sub_o

3、ut=sout); END ARCHITECTURE s8;3-8 设计一个求补码的程序,输入数据是一个有符号的 8 位二进制(原码)数。-解:5-9 设计一个求补码的程序,输入数据是一个有符号的 8 位二进制数。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY org_patch ISPORT( org_data : IN STD_LOGIC_VECTOR(7 DOWNTO 0);-原码输入patch_data : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);-补码输出END org_patch;ARCHITECTURE BHV OF org_patch ISBEGINPROCESS(org_data)BEGINIF(org_data(7)=0) THENpatch_data=0,补码=原码。elsepatch_data=4 THEN G_40); -计数器异步复位 ELSIF CLKEVENT AND CLK=1 THEN -检测时钟上升沿IF EN=

《eda技术实用教程课后答案---潘松-黄继业》由会员小**分享,可在线阅读,更多相关《eda技术实用教程课后答案---潘松-黄继业》请在金锄头文库上搜索。

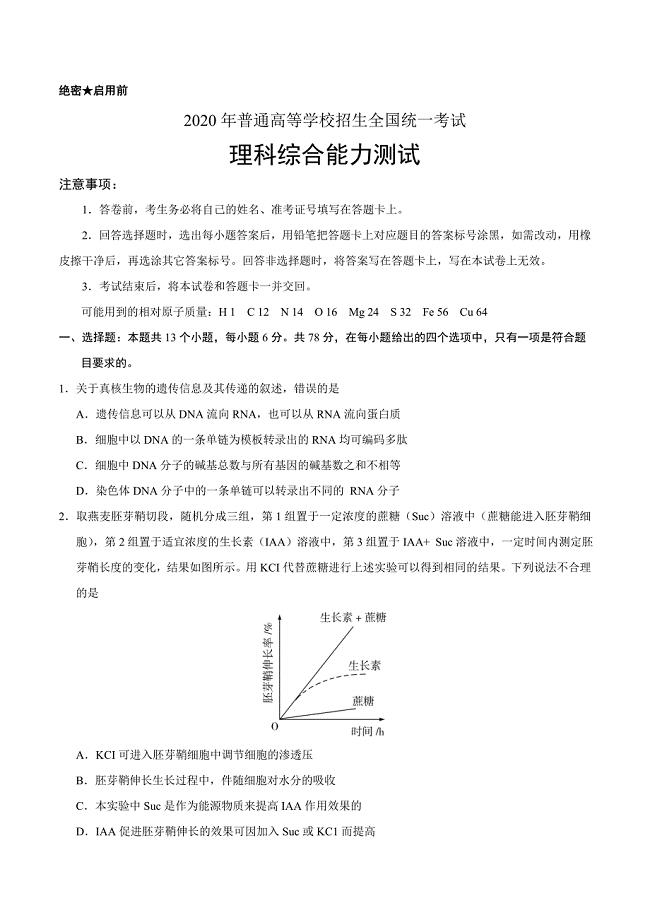

2020年高考真题——理科综合(全国卷Ⅲ)+Word版含答案

2021年绝味鸭脖策划书

2021年熟食店创业方案

2021年熟食店开店策划

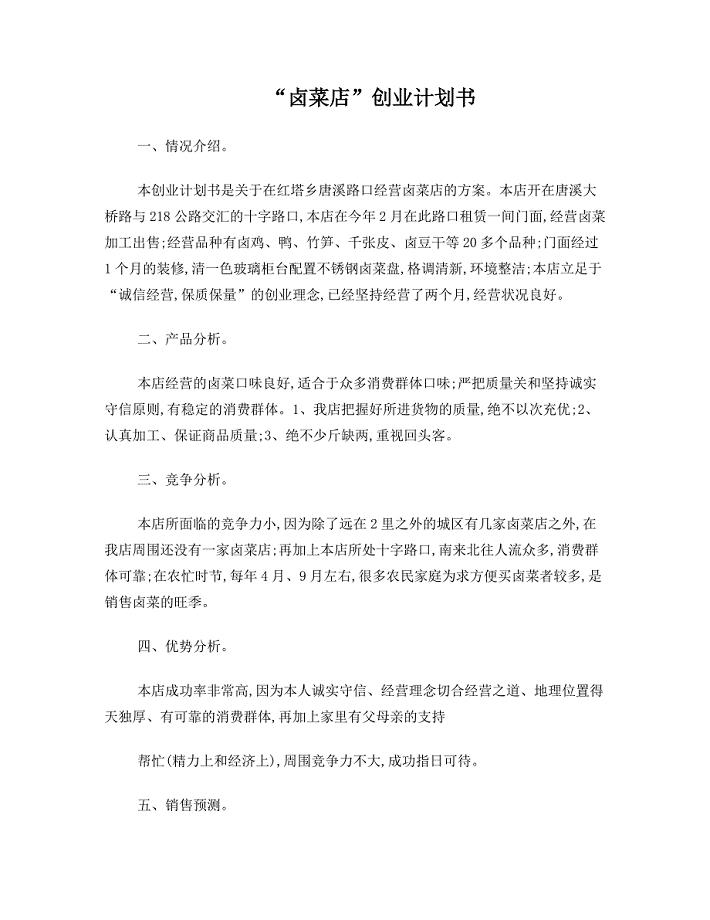

2021年卤菜店创业计划书

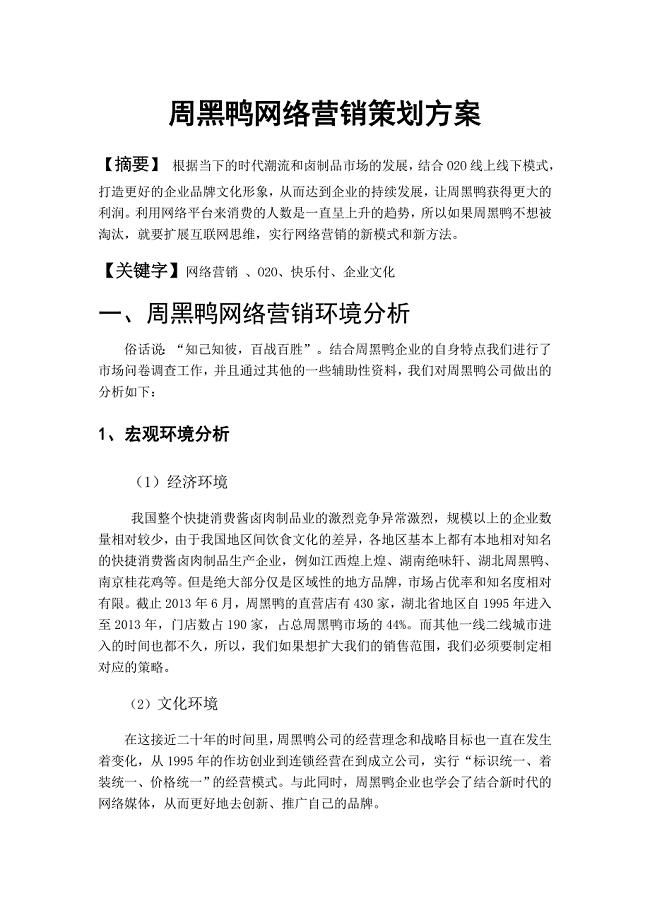

2021年周黑鸭网络营销策划方案

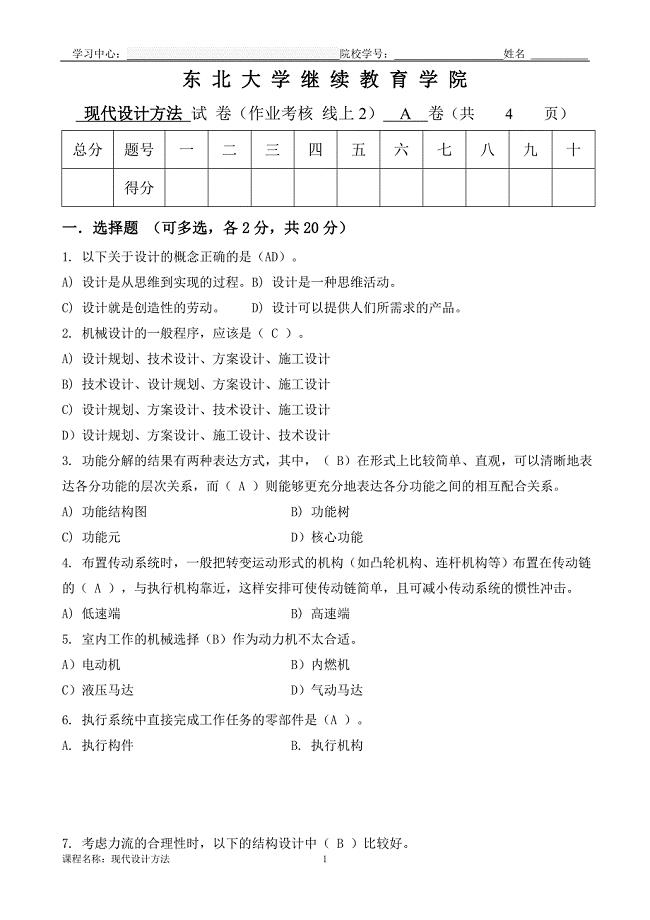

东大21年1月考试《现代设计方法》考核作业

谈我国行政管理效率的现状及其改观对策(论文)

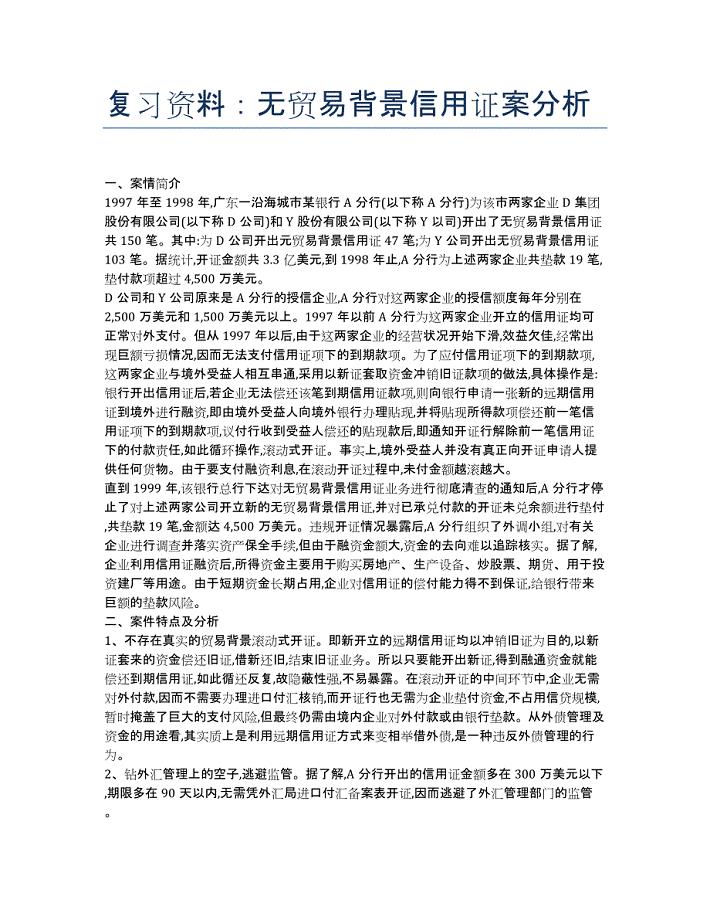

单证员考试-备考辅导-复习资料:无贸易背景信用证案分析.docx

土木工程毕业生答辩自述.docx

建筑学毕业后工作状态真实写照.doc

C#代码规范(湖南大学).doc

xx区食药监局2019年工作总结及2020年工作计划

2019年中医院药物维持治疗门诊工人先锋号先进事迹

2019年度xx乡镇林长制工作总结

2019年性艾科工作计划书

2019年人才服务局全国扶贫日活动开展情况总结

关于组工信息选题的几点思考

摘了穷帽子 有了新模样

2019年某集团公司基层党支部书记培训班心得体会

09.石油公司制度体系诊断及优化咨询项目

09.石油公司制度体系诊断及优化咨询项目

2024-04-08 33页

职工教育培训经费管理办法(规模生产制造业版)

职工教育培训经费管理办法(规模生产制造业版)

2024-04-08 10页

08.圆通银行战略咨询项目

08.圆通银行战略咨询项目

2024-04-08 25页

企业培训费管理实施暂行细则

企业培训费管理实施暂行细则

2024-04-08 12页

职工教育培训经费管理办法(适合中小企业)

职工教育培训经费管理办法(适合中小企业)

2024-04-08 10页

企业规章制度框架体系管理规定(2024修订版)

企业规章制度框架体系管理规定(2024修订版)

2024-04-08 21页

05.景宏集团全面管理提升咨询项目

05.景宏集团全面管理提升咨询项目

2024-04-08 40页

07.玉兔食品集团供应链咨询项目

07.玉兔食品集团供应链咨询项目

2024-04-08 34页

04.大华乳业业务战略咨询项目

04.大华乳业业务战略咨询项目

2024-04-08 28页

06.德邦公司精益生产管理咨询项目

06.德邦公司精益生产管理咨询项目

2024-04-08 28页