内存储器及其接口

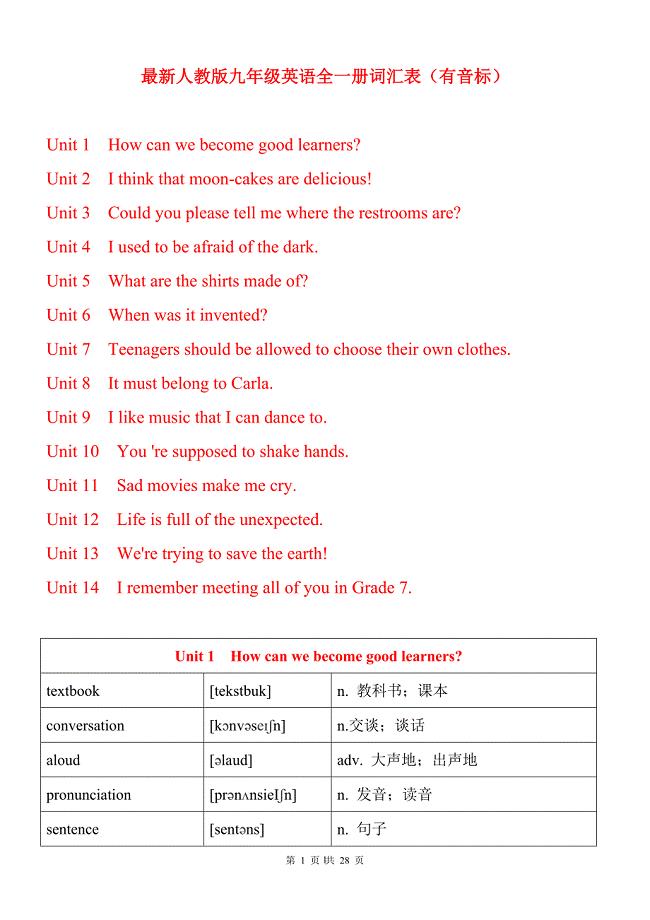

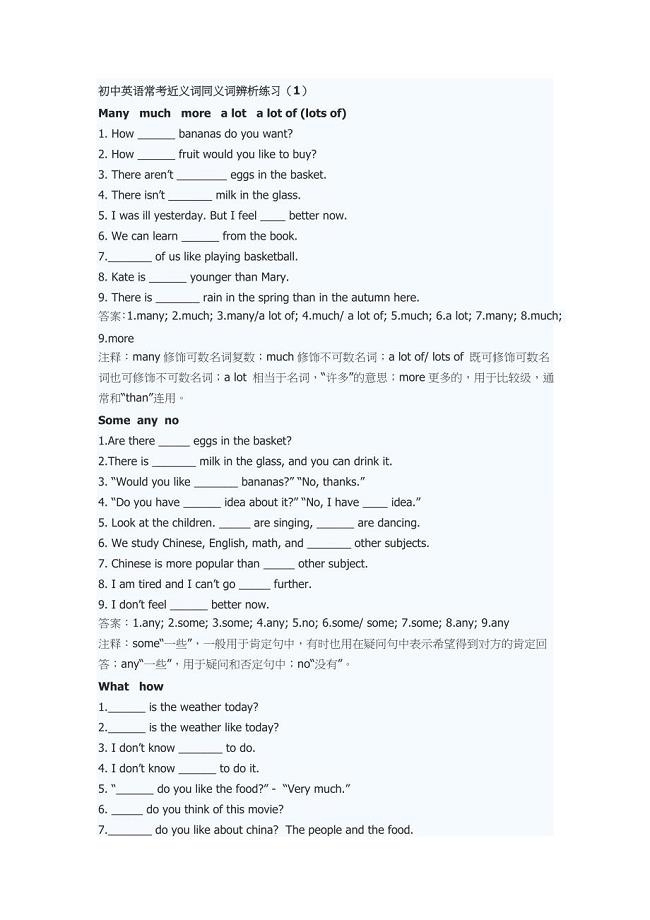

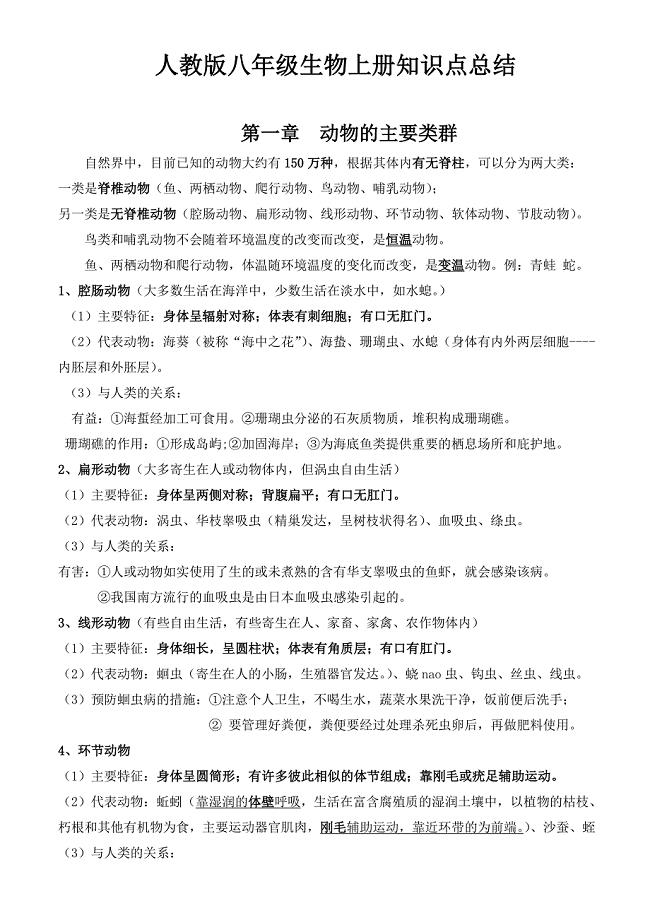

44页1、 第五章 内存储器及其接口5.1 半导体存储器5.1.1 概述5.1.2 RAM芯片的结构、工作原理及典型产品5.1.3 ROM芯片的结构、工作原理及典型产品 5.2 半导体存储器接口的基本技术5.2.1 8位微机系统中的存储器接口5.2.2 动态存储器的连接*(超出大纲范围,自 学)5.1 半导体存储器5.1.1 概述存储器是信息存放的载体,是计算机系统的重要 组成部分。有了它,计算机才能有记忆功能,才能把 要计算和处理的数据以及程序存入计算机,使计算机 能脱离人的直接干预,自动地工作。存储器就是用来存储程序和数据的,程序和数据都 是信息的表现形式。按照存取速度和用途可把存储器 分为两大类:内存储器(简称内存,又称主存储器) 和外存储器。存储器的容量越大,记忆的信息也就越 多,计算机的功能也就越强。一、内存储器的基本结构图5-1 存储器的逻辑结构示意图0000H 0001H 0002H XXXXH 读写控制总线 N位数据总线 地址译码器地址 内容 M位地址总线 存储体MB数据寄存器 MDR地址寄存器 MAR二、存储器中的数据组织 在计算机系统中,作为一个整体一次存放或取出内存 储器的

2、数据称为“存储字”(8位机的存储字是8位,即 一个字节;16位微机的存储字是16位,两个字节;32 位微机的存储字是32位,四个字节等等) 在现代计算机系统中,特别是微机系统中,内存储器 一般都是字节编址的。 一个8位存储字对应一个8位的字节单元;一个16位存 储字对应两个8位的字节单元;一个32位存储字对应四 个8位的字节单元;存储字地址是以1、2、4个存储单 元中最低端的单元地址作为存储字地址。三、半导体存储器的重要性能、技术指标(1)存储容量 (2)存储速度 (3)可靠性存储容量是指存储器可以容纳的二进制 信息量,以2M*N位表示。M表示存储器 地址线的位数,N表示存储器的数据线的 位数。容量为 : 211*8= 2KB四、半导体存储器的分类 半导体存储器按类型可分为随机存储器 (RAM)和只读存储器(ROM) 1RAM的种类:在RAM中,按工艺可分为双极 型和MOS型两大类。用MOS器件构成的RAM ,可分为静态RAM和动态RAM两种。 2ROM的种类:1)掩膜ROM;2)可编程的 只读存储器PROM;3)可擦除的EPROM;4 )电擦除的E2PROM;5)快速擦写存储器 Fl

3、ash Memory 又称快闪存储器1.随机存取存储器RAM RAM的特点是存储器中信息能读能写, RAM中信息在关机后立即消失。它又可分 为静态RAM(SRAM)和动态RAM(DRAM)(1)SRAMSRAM的特点是只要电源不撤除,写入SRAM 的信息将不会消失,不需要刷新电路(2)DRAM写入DRAM的信息的保存时间为2ms左右,为 了保存DRAM中的信息,每隔12ms要对对其 刷新一次。一般微机系统统中的内存都采用 DRAM。图5-2 半导体存储器的分类图5.1.2 RAM芯片的结构、工作原理及典型产品一、RAM芯片的内部结构图5-3 典型的RAM的示意图1 2 31 32 1 2 31 32 读/写 选片 数据输入 A5 A6 A7 A8 A9 1 2 31 32 1 2 31 32 32321024 存储单元 译 码 器 地 址 反 相 器 A0 A1 A2 A3 A4 驱 动 器 I/O电路 Y 译码器 地址反相器 控制 电路 输出 驱动 数据输出1.SRAM(静态)的存储器单元基本存储电路单元(六管静态存储电路)A BVCC (+5V)T1T2T3T4图5-4 基本存储电

4、路单元(位)X 地址译 码线 D0 DO (I/O) 接 Y 地址译码器 (I/O) T6 T5 VCC ( +5V ) A B T1 T2 T3 T4 T7 T8 2.动态RAM的存储单元(单管动态存储电路)CD数据线 CS0.2V 字选线 TS 图5-5 单管动态存储电路 二、RAM典型芯片举例1. 常用典型的(静态)SRAM芯片有6116、6264、 62256等。A7 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 GND VCC A8 A9 WE OE A10 CS D7 D6 D5 D4 D3 1 24 2 23 3 22 4 21 5 20 6 19 7 18 8 17 9 16 10 15 11 14 12 13 图5-6 6116引脚 6264引脚 NC A12 A7 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 GND VCC WE CS2 A8 A9 A11 OE A10 CS D7 D6 D5 D4 D3 1 28 2 27 3 26 4 25 5 24 6 23 7 22 8 21 9 20 10 19 11 18 12 17 13

《内存储器及其接口》由会员206****923分享,可在线阅读,更多相关《内存储器及其接口》请在金锄头文库上搜索。

人教版小学英语单词分类记忆汇总表excel版

人教版九年级全一册英语词汇

2019年开展垃圾分类的工作总结报告【五篇】

六年级英语绘本教案

外研版小学英语单词表全带音标(一年级起点1-12册)

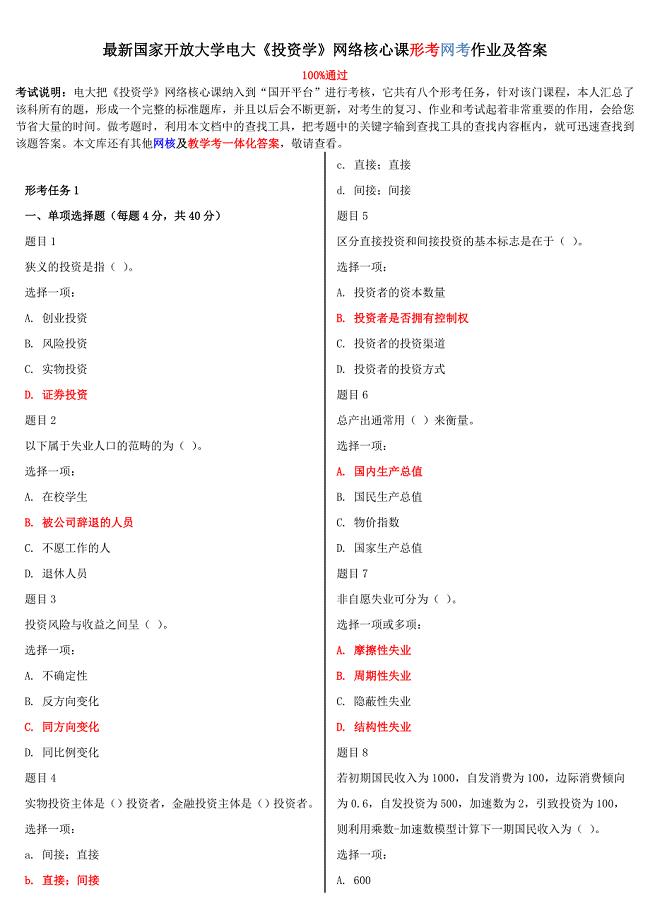

最新国家开放大学电大投资学网络核心课形考网考作业及答案

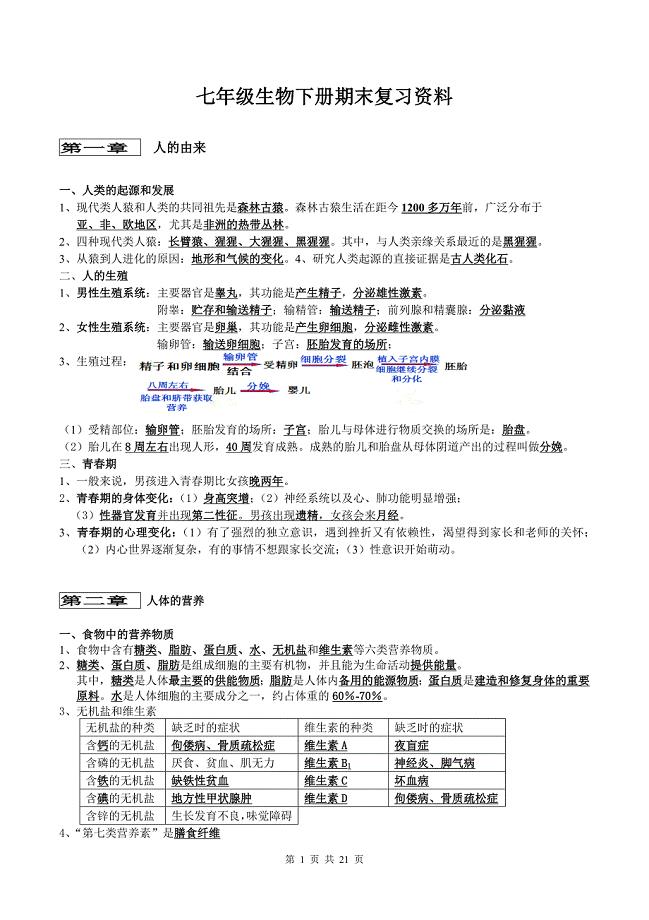

初中人教版七年级下册生物复习提纲

高中英语语法大全高中英语语法系统全解word版

☆初中英语语法专项练习习题以及答案

初中英语常考近义词同义词辨析

高中物理选修3-5全套教案(人教版) (1)

英语绘本《WeatherReport》教学设计

防护功能平战转换设计专篇各专业

初中人教版七年级上册下册全册生物复习提纲21页 (1)

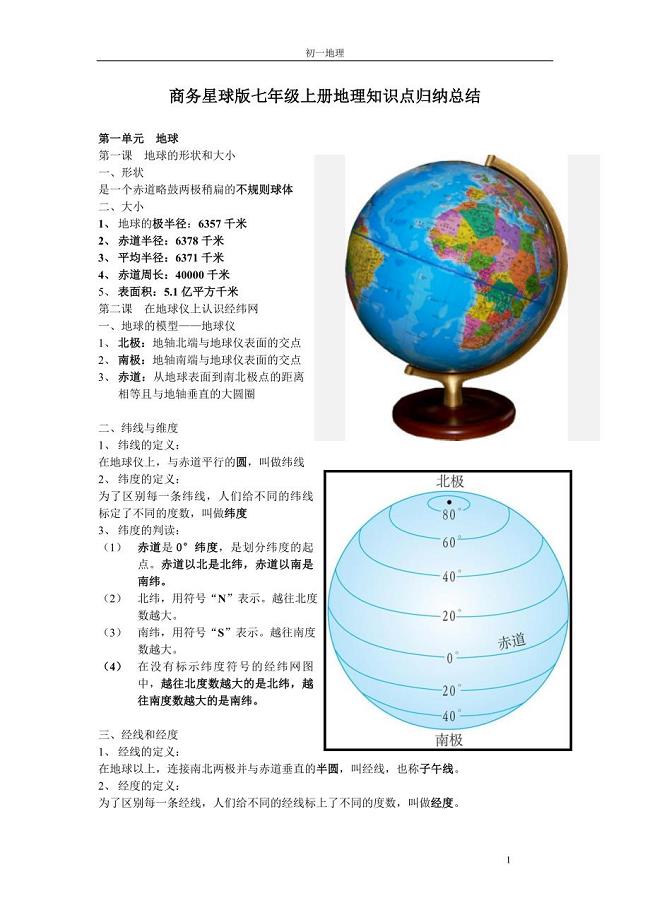

商务星球版七年级上册地理知识点归纳总结

初中人教版七年级上册下册全册生物复习提纲21页 (2)

高中高考语文作文词汇句型优美句子万能语句大全

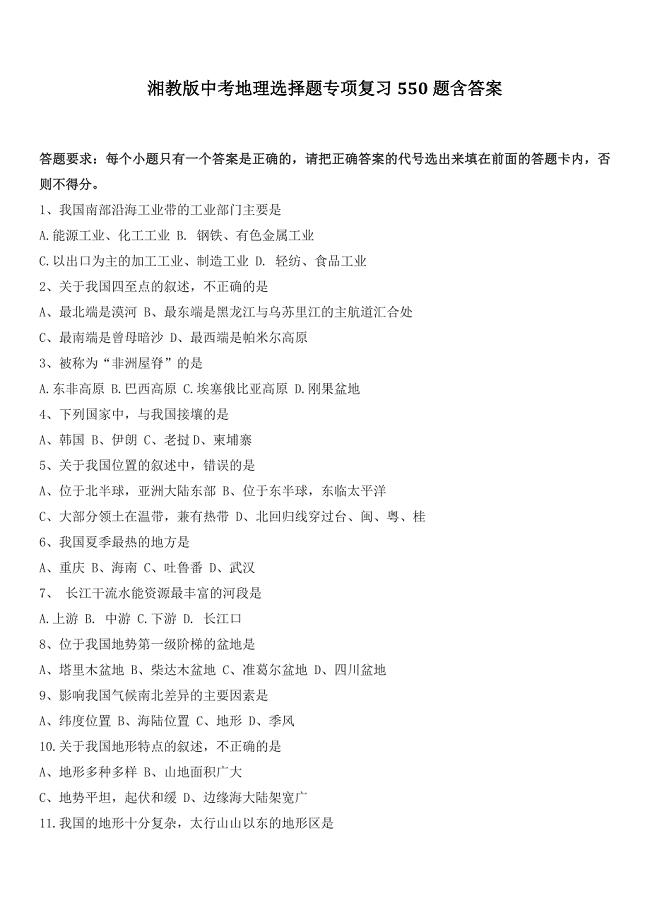

中考地理选择题专项复习550题含答案

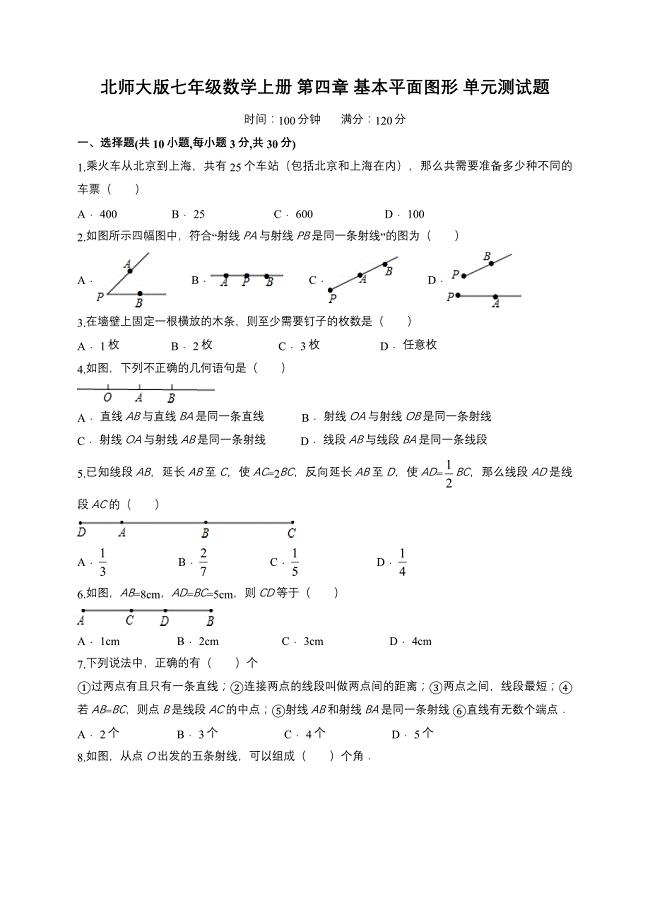

北师大版七年级数学上册第四章基本平面图形单元测试题含解析

人教版七年级数学上册第一章有理数单元检测题解析版

apqp 第3版 & 控制计划 第1版

apqp 第3版 & 控制计划 第1版

2024-04-08 20页

消防器材及巡查要点

消防器材及巡查要点

2024-04-06 36页

推动未来产业创新发展PPT课件

推动未来产业创新发展PPT课件

2024-02-09 36页

职业病危害专项治理

职业病危害专项治理

2024-01-31 31页

实现社会主义现代化和中华民族伟大复兴

实现社会主义现代化和中华民族伟大复兴

2024-01-28 18页

小学高年级读本教学建议

小学高年级读本教学建议

2024-01-28 31页

小学高年级读本编写思路和主要内容介绍

小学高年级读本编写思路和主要内容介绍

2024-01-28 24页

筑牢坚不可摧的钢铁长城

筑牢坚不可摧的钢铁长城

2024-01-28 27页

初中读本内容说明

初中读本内容说明

2024-01-28 24页

党和人民心连心

党和人民心连心

2024-01-28 25页