选题3基于FPGA的计算器设计

16页1、选题3 实验讲义实验名称:基于FPGA的计算器设计1 基于VHDL的运算系统设计原理分析本设计是基于VHDL的运算系统设计,目的是为了实现4位BCD码的加、减、乘、除的运算功能。运算时能够通过键盘输入运算类型和运算所需要的数据,然后通过BCD码转二进制电路将数据转化成运算所需要的二进制数,再将数据和运算类型反馈到相应的运算电路得到运算结果,最后将运算结果通过译码电路传送给数码管将结果显示出来。整个设计过程是在Quartus 的环境中进行的,采用自顶向下的设计方法,系统的结构框图如图2-1所示。图2-1 系统结构框图2 加法器设计 为了能够实现4位BCD码的加法运算,设计中被加数和加数都为16位二进制数,由于2个16位二进制数相加可能会产生进位,同时为了方便数码管显示,和采用了20位二进制。此外还有清零信号rst和加法使能信号add,当rst=1时对和进行清零,否则当add=1时进行加法运算。3 减法器设计 为了实现4位BCD码的减法运算,设计中被减数和减数为16位二进制数,差为20位二进制数。输入的信号有清零信号rst、减法使能信号sub、被减数a、减数b,输出的信号有差cha和借位c

2、o。由于两个数相减的差有可能为正数也有可能为负数,当差为负数时表现为补码的形式,必须要将负数的补码进行修正,修正时对差的低16位求补码运算,而差的正负用借位co来表示,co=1表示差为负,否则为正。4 乘法器设计4.1 乘法器设计的原理分析乘法运算的方法可以通过以下实例来说明:设被乘数A=1110,乘数B=1101,求AB。由以上实际例子可以看出,16位二进制乘法运算可以使用移位相加的方法来实现,被乘数左移16次,乘数右移16次,当时钟上升沿到来时都对乘数的最低位进行判断,如果乘数的最低位为1则乘积加上已经移位的被乘数,否则加0。4.2 乘法器电路结构框图 根据乘法原理,采用移位相加的办法来实现乘法运算,如图5-1。图5-1 乘法器设计结构框图4.2.1 乘法器控制电路设计由于此次设计的是16位二进制乘法器电路,被乘数和乘数必须要移动16次,因此必须要使时钟信号只有16个脉冲。控制电路采用计数的办法,当乘法运算使能信号mul=1时,将计数值cnt16b清零,否则当cnt16b小于16时,cnt16b加1且cp等于clk;否则cp等于0,这样就保证了cp输出只有16个脉冲。关键的VHDL

3、程序如下:process(clk,mul)-描述了一个移位脉冲计数器,产生移位脉冲 begin if mul=1 then cnt16b=00000; elsif clkevent and clk=1 then if cnt16b16 then cnt16b=cnt16b+1; end if; end if; end process;process(clk,cnt16b,mul)begin if mul=0 then if cnt16b16 then cp=clk; else cp=0; end if; else cp=clk;end if;end process;4.2.2 乘数右移电路设计乘数右移的目的是为了判断乘数的最低位是0还是1,如果为0则乘机加上移位后的被乘数,否则加上0。关键的VHDL程序如下:process(clk,mul)begin if clkevent and clk=1 then if mul=1 then shifter16=multiplier;-当 mul=1装载入乘数 else shifter16(14 downto 0)=shifter16(15 do

4、wnto 1);-将乘数右移一位 end if; end if; qb=shifter16(0);end process;4.2.3 被乘数左移电路设计 被乘数左移在乘法运算中是必须的,根据乘法运算的原理,当乘数的最低位为1时左移后的被乘数作为加法电路的一个加数。当乘法运算使能信号mul为1时,在被乘数前添加16个0,之后当脉冲到来的时候左移一位。关键的VHDL程序如下:process(mul,clk)begin if mul=1 then seg8=0000000000000000&multiplicand;-当mul=1在被乘数前添加16个0 elsif clkevent and clk=1 then seg8(31 downto 1)=seg8(30 downto 0); seg8(0)=0; end if;end process;4.2.4 加法电路 加法电路负责判断右移后的乘数的最低位是0还是1,如果是1则将乘积和左移后的被乘数相加,否则加0。当乘法运算使能信号mul为1时,乘积初始化为0。关键的VHDL程序如下: process(mul,clk)beginif mul=1

《选题3基于FPGA的计算器设计》由会员油条分享,可在线阅读,更多相关《选题3基于FPGA的计算器设计》请在金锄头文库上搜索。

最新学校新冠肺炎疫情突发事件应急处置办法和流程

最新疫情防控期间学校用餐与食堂管理规定和师生一日流程图

最新Xx省xx区返学师生员工健康登记表

诊所简介

高中英语-第二单元-《the-United-Kingdom》课件-新必修5

新版新目标英语七年级下unit4--Don't-eat-in-class课件

新版PEP六年级英语unit6-how-do-you-feel-A-Let's-talk

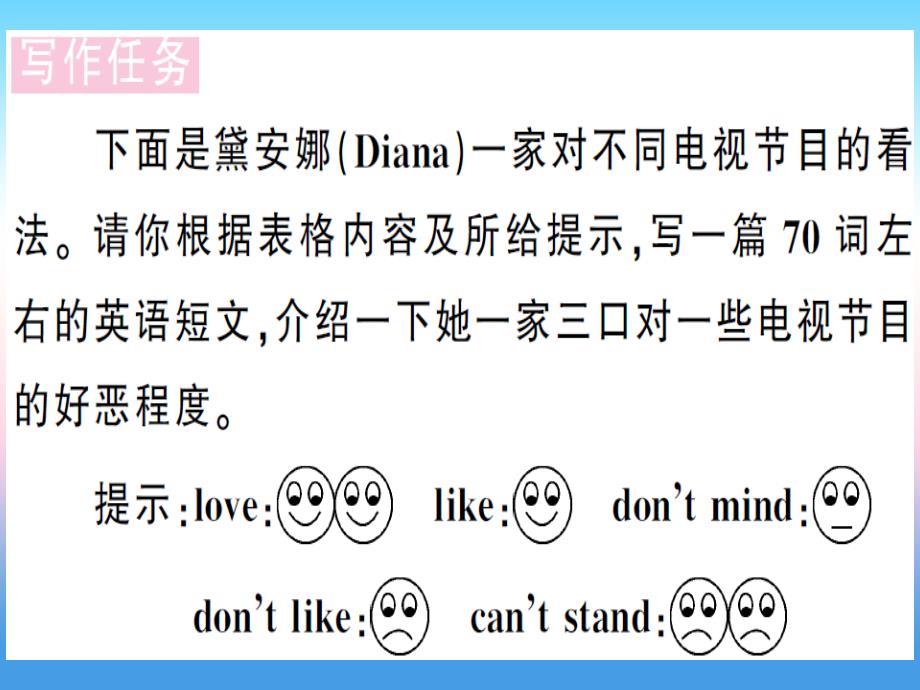

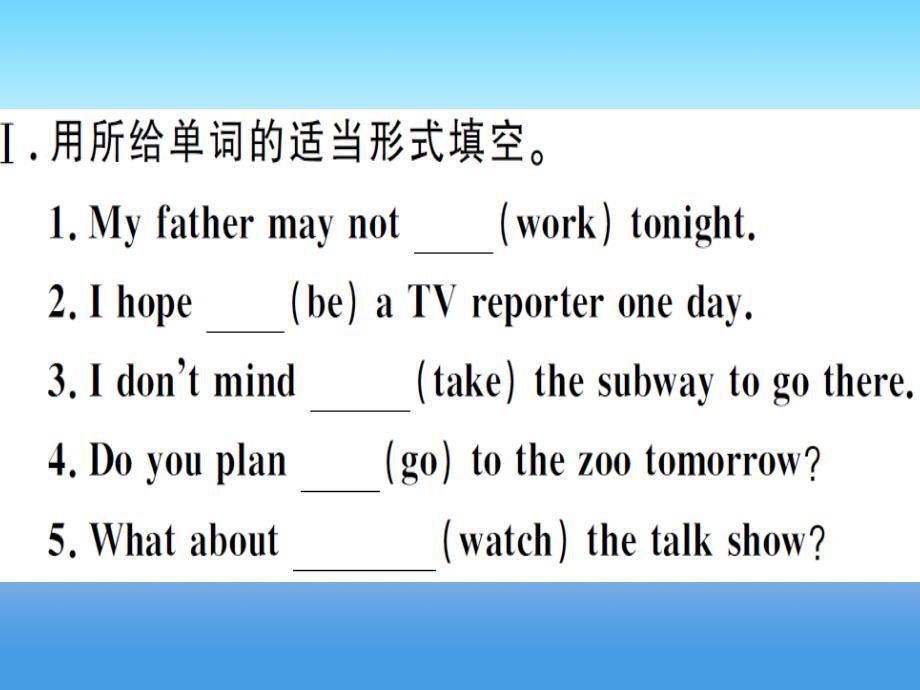

安徽专版2018秋八年级英语上册Unit5Doyouwanttowatchagameshow第6课时习题课件新人教目标版

酸的和甜的教学课件.doc

Lesson-1-Where-do-we-go-from-here概要

Docker技术与实践

七年级英语下册-Unit-9-What-does-he-look-like(第3课时)(Grammar-Focus-3d)同步语法精讲精练课件-(新版

《I'm-going-to-do-the-high-jump》PPT课件3

高二英语外研版-必修5-Module-2-A-Job-Worth-Doing-Reading课件

英语片段教学-I-can-do-it

Adobe公司简介

安徽专版2018秋八年级英语上册Unit5Doyouwanttowatchagameshow第2课时习题课件新人教目标版

第二单元全课件Unit2-What-time-do-you-go-to-school-全课件

第18课-Windows的磁盘管理与安全

第12章--Windows-Server-2008路由及远程访问

小数数学题:简便计算11道练习题及参考答案A10

小数数学题:简便计算11道练习题及参考答案A10

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A7

小数数学题:简便计算11道练习题及参考答案A7

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A3

小数数学题:简便计算11道练习题及参考答案A3

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A5

小数数学题:简便计算11道练习题及参考答案A5

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A9

小数数学题:简便计算11道练习题及参考答案A9

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A6

小数数学题:简便计算11道练习题及参考答案A6

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A8

小数数学题:简便计算11道练习题及参考答案A8

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A1

小数数学题:简便计算11道练习题及参考答案A1

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A4

小数数学题:简便计算11道练习题及参考答案A4

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A2

小数数学题:简便计算11道练习题及参考答案A2

2024-04-17 2页